基于USB2.O的轨道电路信号车载采集与分析系统

摘要:介绍了一种基于USB2.O的车载采集与分析系统,详细设计了系统的硬件和软件。硬件方面通过对CY7C68013的通用可编程接口(GPIF)控制逻辑的合理设计和芯片内部FIFO的有效运用,实现了在USB设备和主机之间大量数据的高速传输。软件方面采用模块化设计实现了信号的数字滤波、频谱分析、波形显示、存储以及回放。

关键词:数据采集;数字信号处理技术;USB

0 引言

近年来,随着铁路建设的跨越式发展,对机车信号检测的准确性和可靠性提出了越来越高的要求,传统的手持式信号检测系统已经远远不能满足需要,本文提出的车载信号采集系统采用数字信号处理(DSP)技术实现对机车信号波形的频谱分析。利用可靠的硬件和软件技术实

现机车信号检测的实时性和高精度要求。系统采用USB总线接口有效地解决了传统总线形式(如RS232、并口、ISA等)传输速度低、安装繁琐、易受机箱内环境的干扰、计算机系统资源限制等缺点,具有廉价、高速、支持即插即用、使用维护方便等优点。

1 系统总体设计

本数据采集系统的设计主要分为硬件和软件设计两部分。其中硬件设计主要包括信号调理、A/D转换、数据存储、控制部分以及USB接口部分等实现内容。

系统软件设计分为USBN件(Firmware)、USB设备驱动程序以及主机应用程序三部分内容。在Windows操作平台下,主机应用程序通过USB设备驱动程序与系统硬件接口USBDI(USBDeviceInterface)进行通信,然后由系统产生USB数据的传送动作。固件则是运行在接口芯片中的代码,用以响应各种来自系统的USB标准请求,完成数据的交换工作和事务处理。系统结构框架图如图1所示。

2 系统硬件设计

USB数据采集板硬件电路设计实现共分为5大部分,它们分别是信号调理、A/D转换、数据存储、控制部分以及USB接口部分。

2.1 信号调理

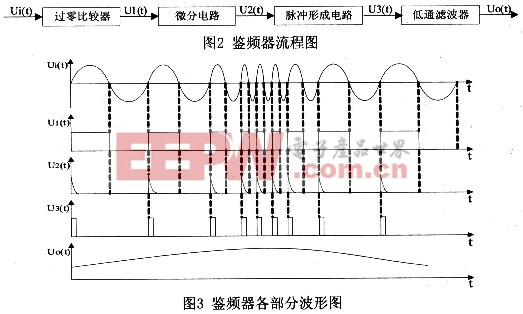

信号调理部分由脉冲计数式鉴频器完成。它由四部分组成(如图2所示),即过零比较器、微分电路、脉冲形成电路和低通滤波器,输入的调频波Ui(t)经过零比较器后变成调频方波信号U1(t),调频方波信号通过微分电路后变为微分脉冲序列U2(t),微分脉冲序列经过脉冲形成

电路后变为等脉宽的方波脉冲序列U3(t),等脉宽的方波脉冲序列通过低通滤波器后就输出调制信号Uo(t)。鉴频器各部分的波形如图3所示。

|

2.2 主控芯片的工作方式

本设计采用的主控芯片是Cypress公司的USB2.0控制芯片CY7C68013,它与计算机通过USB接口相连,使设备能在PC机的控制下进行操作。USB主控芯片通过逻辑控制电路连接到FIFO和A/D转换后的数据传送至FIFO芯片进行缓冲,缓冲后的数据输入主控芯片的从FIFO中,

然后从FIFO以DMA(直接内存存取)的方式经由SIE(串行接口引擎)传给PC机。

为了实现高速数据采集的功能,A/D芯片采用的ADl674,它是一款12位,最高转换速度可达100kHz的A/D转换芯片,考虑到对FIFO容量的需求,系统采用GPLD和FIFO来实现。选用IDT7205完成数据缓存。其最高工作频率为133MHz,容量为8kB,能满足设计要求。

CY7C68013与外设有两种接口方式:通用可编程接口GPIF方式和从属FIFO方式。GPIF的核心就是一个可编程状态机,可产生6个控制和9个地址输入信号,并能接收6个外部和2个内部“ready”输入信号。GPIF向外部接口产生正确的选通信号和握手信号,外部接口用于对FIFO数据的传进和传出。GPIF是主机的方式,而从属FIFO方式是从机方式,它由外部控制器控制,可像对普通FIFO一样对FX2的多层缓冲FIFO进行读写。FX2的从属FIFO工作方式可设为同步或异步,工作时钟可选为内部产生或外部输入,其它控制信号也可根据需要设置为高有效或低有效。

2.3 FlF0的数据缓存作用

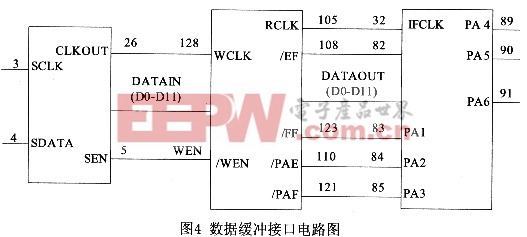

由于A/D最高采样频率可达100MHz,而主控芯片CY7C68013中的FIFO只有4kB,不能满足A/D数据转换器的要求,因此需要在A/D和CY7-C68013之间增加一个高速的FIFO来缓存数据。FIFO是先进先出的数据缓存器,数据在其内部顺序写入、顺序读出,其数据地址由内部读写指针自动加1完成。它具有双口输入输出、采集传送速度快等特点,能满足高速数据传输的要求。由FIFO构成的数据缓冲电路主要部分的接口电路如图4所示。

IDT7205有两种工作模式,即IDT标准模式和FWFT模式。本设计中采用IDT标准模式,这种模式通过FF、PAF、PAE、HF、EF五个标志位来实现数据的传输。/WEN(写使能端)置为有效时,数据可以写入FIFO。在WLCK(写时钟)的控制下,数据持续写入FIFO,当第一个数据被写入时,/EF(空标志)无效,数据不断地写入FIFO,即将写满时/PAE(将空标志)无效,/PAF(将满标志)有效,表示FIFO即将写满。当FIF0写满时,/F

- 采用CompactDAQ平台提高USB数据采集应用的性能(01-17)

- 基于FPGA的USB2.0虚拟逻辑分析仪的设计与实现(01-18)

- 高速串行数据链路的自动化一致性测试(04-15)

- 基于LABVIEW的USB接口多路高速数据采集系统的设计(11-24)

- 基于AVR USB接口的温度测量系统下位机设计(03-01)

- 理解下一代数据采集技术(05-12)