基于USB2_0和DDR2的数据采集系统设计与FPGA实现

摘要: 采用DDR2 SDRAM作为被采集数据的缓存技术, 给出了USB2.0与DDR2相结合的实时、高速数据采集系统的解决方案, 同时提出了对数据采集系统的改进思路以及在Xilinx的Virtex5 LX30 FPGA上的实现方法。

0 引言

随着计算机、微电子和嵌入式系统技术的发展, 数据采集技术已经在生物医学、图像处理、雷达系统等众多领域得到广泛应用。本文设计的高速数据采集系统是应用于芯片现场测试的实时数据采集系统, 由于被测试芯片为250 MHz 8 bit的高速AD输出, 因此, 该数据采集系统的数据采集率是2 Gbps。为了达到实时、高速、海量的数据采集, 该系统利用DDR2 SDRAM的高速数据传输能力和海量存储能力做为采集数据的缓存,然后通过具有即插即用、易扩展、传输速率较高等特点的USB2.0接口来将DDR2 SDRAM中的数据传输到计算机中进行存储和分析。

1 数据采集系统架构

该数据采集系统的总体架构由硬件部分、固件部分和计算机上的USB驱动及应用程序等几大部分组成, 本文完成了硬件和固件部分的设计。

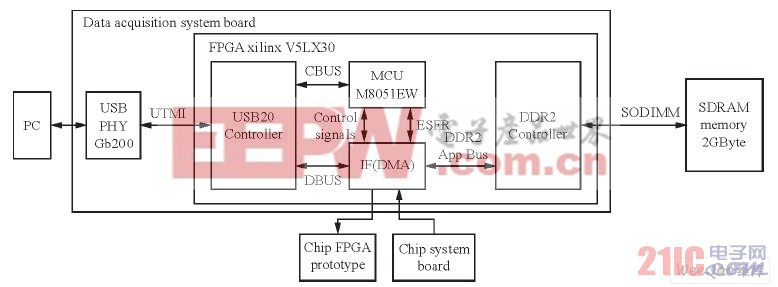

该系统的硬件部分主要由USB2.0、DDR2SDRAM、MCU以及IF等核心模块组成, 图1所示是其系统架构图。

系统总体架构图

图1 系统总体架构图

USB2.0由控制器和物理传输层组成, 其中控制器是在FPGA上实现的Faraday公司的IP核, 物理层可选用SMSC公司的GT3200芯片, 控制器与物理层芯片之间可通过标准的UTMI接口相连。

DDR2 SDRAM控制器是基于Xilinx公司提供的IP核, 工作频率是125~266 MHz, 与SDRAM之间的接口是64 bit SODIMM笔记本内存条接口。作为数据存储的SDRAM 是Samsung 公司的M470T5663QZ3-CE6 2GB 内存条。系统的控制核心MCU采用Mentor Graphics公司的增强型8051 IP核M8051EW, 该8051核采用两个时钟周期为一个机器周期的高性能架构, 同时支持MWAIT信号来控制程序总线, 从而能够支持慢速的外部程序和数据存储器。IF模块是该系统设计的关键, 它相当于DMA的功能, 主要负责USB与DDR2、外部数据接口与DDR2之间的数据传输。

2 数据采集系统设计

本文中的数据采集系统采用USB2.0和DDR2SDRAM相结合的设计思路, 从而打破了传统数据采集系统在实时数据采集中大容量和高速率不可兼得的瓶颈。在图1所示的系统架构的四个部分中, 由于USB2.0和DDR2控制器都是IP核, 因此, 该系统设计的关键在于MCU和IF模块。

2.1 MCU的设计

MCU是数据采集系统的控制核心, 主要用于对USB2.0控制器进行配置、查询和处理USB事务, 以及解析USB设备请求, 同时, 还需配置IF模块, 处理与IF模块之间的控制信号等, 因此,MCU的设计包括数据接口及控制信号的设计以及固件设计两个部分。

MCU数据总线接口包括与USB2.0控制器和与IF模块的接口, 这里的USB2.0控制器和IF模块相当于外部设备挂在MCU的外部存储器总线和ESFR(外部特殊功能寄存器) 总线上。控制信号主要用于计算机上的控制台控制IF模块数据传输的开始与结束, 通常包含在USB的设备请求中。

整个固件的开发可在Keil C下完成, 并可通过JTAG进行调试。开发一般包括三部分: 一是协助USB控制器完成总线列举过程, 让计算机识别USB设备; 二是通过解析自定义USB设备请求,来对采集模式、深度等进行配置, 从而控制采集的开始与结束; 三是查询和处理IN、OUT事务中断, 并控制USB数据传输。

2.2 IF模块设计

IF模块负责接口的转换和数据传输的控制,其结构如图2所示。其中, usb2ddr和eoc2ddr子模块分别控制USB2.0与DDR2 SDRAM、外部采集接口与DDR2 SDRAM之间数据的上下行传输。

上下行数据传输分别由usb2ddr_ctrl 和eoc2ddr_ctrl模块中的状态机进行控制和管理。其中采集模式和深度由MCU的ESFR总线配置, 而传输开始信号则使用MCU的PORT0 [0]、PORT0[1], 结束信号连接在MCU的外部中断NINT0和NINT1上, 这样可使MCU能够及时响应。上行采集开始后, 首先使eoc2ddr_ctrl中的控制状态机处于写状态, 并不断地比较DDR2的地址与配置深度, 直到采集完成。然后再使usb2ddr_ctrl中的控制状态机处于读状态, 同样也比较地址与深度,直到数据读取完成。下行传输过程则与之相反。

IF模块结构框图

图2 IF模块结构框图。

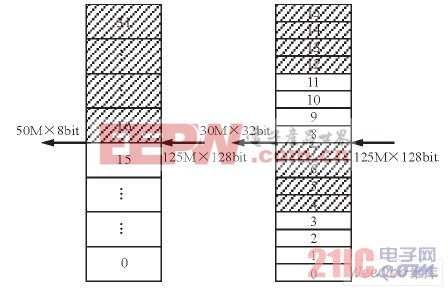

由于各个接口上数据传输的速率不同, 因此, 数据传输时, 要异步FIFO或者缓存。在本设计中, 由于各接口速率固定, 因此, 可采用双端口RAM作乒乓缓存方式以提高效率并保证数据连续, 图3所示是乒乓缓存原理图。

乒乓缓存原理图

图3 乒乓缓存原理图。

当下行发出数据时, 从DDR2的125 M×128bit到50 M×8 bit所需要的最小深度为32×8 bit, 因为从SDRAM中读数据的最大延迟是26个DDR2时钟周期(即208 ns), 而将DDR2读出的128 bit发出则需要16个时钟周期(即320 ns), 因此, 为了保证发出的数据可连续进行乒乓操作, 需要2×128bit的深度。同理, 在上行数据从DDR2的125 M×128 bit到USB的30 M×32 bit则需要4×128 bit深度,因为USB时钟读完128 bit数据需要133.2 ns, 小于SDRAM 读数据延迟的208 ns, 因此, 每次从SDRAM中读2×128 bit数据时, 其乒乓操作就至少需要4×128 bit深度。

3 系统的改进

本数据采集系统对传统的数据采集系统做了创新型改进。改进主要是三个方面: 一是对数据采集的深度实行可配置模式; 二是在功能上不仅作为数据采集系统, 还能作为数据发生器, 即将采集到计算机上的数据通过数据采集系统发送出来; 三是该数据采集系统有两种工作模式, 即普通采集模式和触发采集模式。

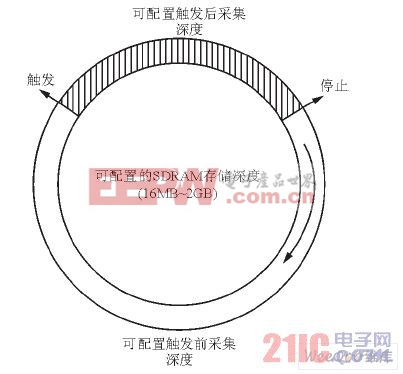

深度可配置增加了系统在使用过程中的灵活性。该系统除了采集数据外, 还能将数据发出来用于芯片的FPGA原型验证, 从而避免了缓慢的大数据量仿真, 更增强了系统的实用性。通过ESFR配置8 bit的深度寄存器可实现以16 MByte为单位的深度调节。触发是数据采集系统不可缺少的功能, 因此, 该数据采集系统分为普通采集模式和触发采集模式。触发采集模式的原理如图4所示。在触发模式中, 可将SDRAM看做一个圆形的循环存储器, 触发前后的采集深度同样也可以通过ESFR配置, 从而实现触发前后的采集深度比例可调。

触发实现机制原理图

图4 触发实现机制原理图。

4 FPGA实现

FPGA在系统设计中具有很好的灵活性和可扩展性, 因此, FPGA是一个非常好的系统实现平台。通过对数据采集系统的资源*估, 可得出如表1所列的资源占用结果。

表1 FPGA的资源占用情况。

FPGA的资源占用情况

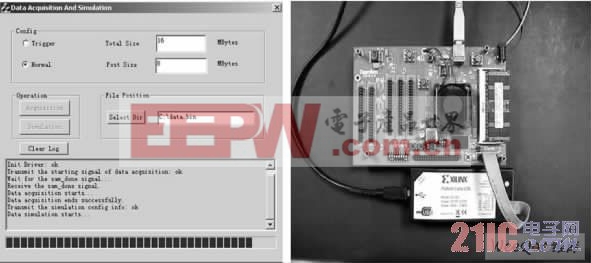

本系统最终选择了Xilinx 公司的FPGA器件Virtex5 LX30。由于DDR2 SDRAM控制器是Xilinx公司的IP核, 故在系统的集成和实现过程中不可避免的要对原IP核进行改动, 同时, 在ISE中布局布线时, 相应地要对原有UCF文件中的约束进行修改, 以满足时序要求。本系统除USB2.0的PHY和SDRAM外, 其余部分均由FPGA实现, 图5所示是系统在计算机上的操作界面和实物图。

操作界面和FPGA实物图

图5 操作界面和FPGA实物图。

5 结束语

本文结合USB2.0与DDR2 SDRAM的特点, 给出了可打破普通数据采集系统在实时、高速和大容量数据采集上的瓶颈的方法, 并且在实用性方面进行了改进。该系统最终可在FPGA上实现,因为用FPGA实现具有极大的灵活性和可扩展性,并且在系统设计成本和快速实现上具有很好的竞争优势。目前, 该数据采集系统在实际运用中效果良好。实际上, 若对采集接口稍加改进, 并将IF模块中的乒乓缓存改为异步FIFO, 就能广泛地应用于各类高速系统的实时数据采集。

- 可测试高数据速率PCIe2.0系统的分析仪/检测仪(05-18)

- 泰克的DDR测试和验证解决方案系列增加两项新功能(11-13)

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)