一种多路同步数据采集系统的设计

。

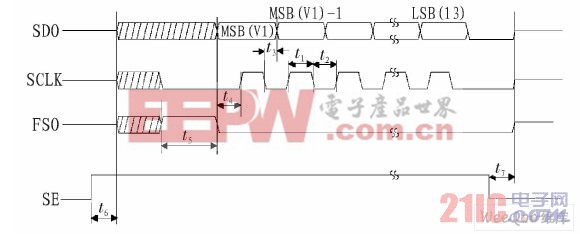

图4 CS5451A串行输出时序图

由于SCLK频率很低,在用CPU的SPI控制器接收数据的时候,CPU接收一位的时间为4tXINe=1μs,如图5所示,一帧数据为96位,接收一帧数据大约为96μs的时间,如果用CPU通过异步FIFO读取数据,因为现在的控制器总线速度很快,假设读一个字节数据需要100 ns,读走一帧数据大约需要100 ns×12=1.2μs(由于MPC8313总线宽度为16位,不能一次读取19位数据,所以在读取FIFO中数据的时候,把通道号锁存到一个暂存寄存器中,读取采样数据后再读取通道号,所以读取一帧数据需要12次)。只有原来的大约1/80的时间,提高了CPU的利用效率。

图5 CS5451A一帧数据输出图

图5 CS5451A一帧数据输出图

4 中断服务子程序的设计

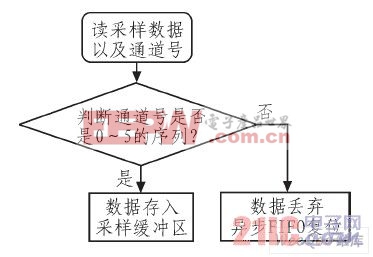

CPU读采样数据是在中断服务子程序中设计的,在中断程序中读走采样值数据,并判断通道号是否对应。软件流程如图6所示。

图6 软件流程图

5 结论

本文利用CS5451A设计一个通用的多路数据采集系统,利用XILINX SPARTAN3E系列FPGA芯片实现异步FIFO和采样数据串并转换模块的设计,CPU不用直接用SPI控制器接收CS5451A芯片输出的串行格式的数据,只需要把ADC输出的串行数据通过串并转换模块存入FIFO缓冲区,并产生一个中断信号,在CPU的中断子程序中读出采样数据。该方案已经在低压继电保护装置中得到了应用,通过试验本系统的数据采集精度可以达到0.2级。调试中发现,在进行PCB设计时,要注意以下几点:

1)模拟部分电路(差分输入以及参考电源部分)和数字部分(XIN、FSO、SDO、SCLK信号)应完全分开在不同的区域里。

2)良好的去耦对抑制CS5451A产生的噪声很重要,去耦电容一般为0.1 μF,且放到电源输入引脚尽可能近的地方,以达到良好的去耦效果。

3)如果系统要求工作在-40~+85℃的温度范围内,要求采样精度达到0.2级,必须使用外部高精度的参考电源。

- 基于C8051F020单片机的多路压力测量仪(01-23)

- 基于FPGA的160路数据采集系统设计(03-22)

- 智能多路信号源的设计与实现(01-10)

- 基于单片机的多路测温仪系统设计(05-09)

- 使用模拟多路复用器的多通道电流测量技术(02-27)

- 用Pico2204A彻底分析视频多路混合器系统的问题(01-12)