多路跟踪滤波同步数据采集系统的研究

介绍了采用高速硬件锁相环技术,对多路相关联信号同时、同步整周期均匀采样和抗混叠跟踪滤波的实现方法。给出了基于此方法由TMS320LF2407和AD73360L构成的多路数据采集与处理系统。提出一种不同结构的同步串行口接口电路的设计方法,给出了电路连接与软件流程。

关键词:数据采集 跟踪滤波 同步采样 抗混叠

目前同步采样实现方法主要有两种,一种是使用多片采样保持器、多路模拟开关和单片单通道逐次逼近型高速A/D转换器,再辅以同步信号产生电路,这样可同时采集多路信号送采样保持器保持,然后通过模拟开关切换分别送入A/D转换器进行转换。该方法使用一片高速A/D转换器实现多路信号同时采样。但外置多片采样保持器及模拟开关使得电路结构复杂、编程麻烦,成本也未能降低。另一种是采用多通道高速逐次逼近型A/D转换器,但16位以上的高速并行A/D转换器通常为单通道或2通道,且价格昂贵。要实现多路(6路以上)信号同时采样,则需要多片ADC,使得成本大大增加。

以上两种方法采用的ADC的转换速度通常在10μs甚至5μs以下,对于工频电参数测量实际上有些浪费,在ADC转换速度能够满足采样频率和数值处理要求的条件下,分辨率、线性度、抗干扰能力及量化噪声等指标对于测量精度显得尤为重要。本文设计采用一种基于6通道独立采样的16位串行Σ-ΔA/D转换器AD73360L,构成多路相互关联信号同时、同步采样的数据采集系统,并且具有跟踪输入信号频率变化,抗混叠滤波的功能。内部6个通道可同时采样,无须CPU干预,从而有效地减少了由于采样时间不同而产生的相位误差,非常适合三相电压、电流的采样,且高达64kHz的采样率完全能够满足电力参数测量要求。AD73360L还能多片级联使用,使模拟量输入通道的最大数目方便地扩展至48路。另外,AD73360L还有内置的程控可变增益放大器, 增益可在0~38dB之间选择,因而它既适合于大信号的应用,也适合于小信号的应用[1]。

本文详细介绍AD73360L与TMS320LF2407 DSP组成的同步采集系统的工作原理及不同结构的同步串行口的接口电路设计方法。

1 同步数据采集系统硬件结构与工作原理

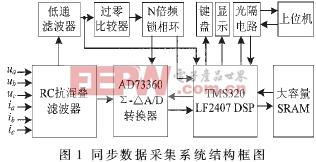

同步数据采集系统由三部分组成,其结构框图如图1所示。第一部分由抗混叠滤波电路和Σ-△A/D转换器AD73360L组成,6路输入信号经过RC抗混叠滤波处理后进入6通道Σ-△A/D转换器。第二部分是由低通滤波器、过零比较器和倍频锁相电路组成的同步采样信号发生电路。它产生N倍于测量信号频率的方波信号作为采样信号,控制A/D转换器同步采样和数字滤波。第三部分由DSP、SRAM、键盘、显示和光隔控制等电路组成,实现对A/D转换结果的高速读取、数据处理、存储、显示和上传数据给上位机等。

1.1 Σ-ΔADC内部结构与工作原理

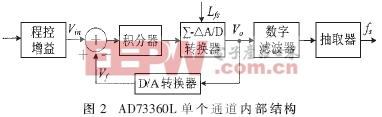

AD73360L的每个独立的A/D转换通道的内部结构如图2所示。经程控放大器调理后的输入信号Vin与反馈信号Vf相减后的增量再经采样保持器保持后输入A/D转换器,低分辨率A/D转换器以Lfs=DMCLK/8的高过采样率对保持后的增量进行高速采样,16位累加器对低分辨率采样值累加求和后得到高分辨率的Vo,再由D/A转换器转换成16位模拟量Vf反馈到减法器,从而形成闭环负反馈的Σ-ΔA/D调制器。通过负反馈环路的不断调整使Vo(N)=Vo(N-1)+[Vin-Vf (N-1)],即Vo(N)=Vin。由于A/D转换器在量化过程中存在量化误差,但通过闭环负反馈环路的误差补足性能和高速重复取样方法,把量化噪声延续到Lfs/2的整个频带范围内,并将它推到正常采样率以外的高频段上[2]。

抗混叠数字滤波器对2K个高速采样值Vo进行数字均值滑动滤波(抽取系数K=高过采样率/采样率),滤除二分之一采样频率以上的高频噪音和输入信号的高次谐波。滤波特性的详细描述参见文献[1]。经滤波后的采样值按K:1抽取作为输出,降低了A/D转换通道的采样率,从而降低了同步串行口的速度要求。A/D转换通道的采样频率fs=Lfs/K。时钟频率与高过采样率、采样率和抽取系数K均存在整倍数关系,提供了控制Σ-ΔADC实现同步采集、跟踪滤波的条件。

1.2 同步采样的实现方法

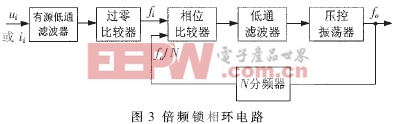

当采样速率是被测信号频率的整倍数,采样点包含整个周期,且满足采样定理时,用DFT频谱分析,频域不会发生泄漏,可完全消除误差[2]。因此采用硬件锁相环电路产生整倍于被测信号频率的方波来控制Σ-ΔA/D转换器实现同步整周期采样。倍频锁相电路如图3所示。

为使锁相环准确锁定在被测信号(ui或ii)的基波频率上,输入电压信号经3阶有源低通滤波器滤除60Hz以上高次谐波,经过零比较器输出对称方波,作为高速锁相环的输入信号fi。fi同时也用作DSP测量信号频率的信号源。

被测信号频率fi与反馈信号fo/N进行相位比较,其相位差信号经过低通滤波后,控制压频振荡器输出频率fo发生相应的变化,再经N分频后反馈到相位比较器,通过负反馈环路的快速调整,最终达到环路锁定。锁定时fo/N与fi的频率之差趋于零,即fo=Nfi。将锁相环产生的倍频信号fo作为Σ-ΔA/D转换器的主时钟信号,可以控制Σ-ΔA/D转换器实现同步数据采集[3-4]。

被测50Hz信号每周期采样1 024次,则采样率fs为51.2kHz,压控振荡器中心频率fo=fs×256=13.1 072(MHz)。压控振荡器上、下限频率设计为16MHz和10MHz,当被测信号在60~40Hz范围变化时,可以实现同步数据采集。同步采样率可通过编程选择每周期采样1 024、512、256和128次。

锁相环电路由高速锁相环芯片74HC4046A和分频器CD4060组成,产生AD73360L采集触发信号,74HC4046A压频振荡器最高输出频率可达24MHz。

1.3 跟踪滤波的实现方法

由于Σ-ΔA/D转换器实现同步采集,采样频率始终是被测信号频率的整倍数。由Σ-ΔA/D转换器的原理可知,抗混叠数字滤波器对2K个高速采样值Vo进行数字均值滑动滤波,滤除被测信号中二分之一采样频率以上的高次谐波。因此,抗混叠数字滤波器的截止频率始终跟踪信号频率变化,使它具有良好的抗混叠跟踪滤波功能。

1.4 模拟输入前端电路设计

由于采用Σ-Δ A/D转换原理,具有良好的内置抗混叠性能,所以对模拟前端滤波器的要求不高,用一阶RC低通滤波器就能满足要求[5],从而省去由开关电容滤波器和复杂外围控制电路组成的抗混叠跟踪滤波电路,节省了成本。为了提高系统抗干扰能力,模拟输入通道采用差动输入方式,具体电路如图4所示。输入信号通过C1和C2耦合到ADC的模拟输入端。R1和C3、R2和C4构成一阶低通抗混叠滤波器。图中REFOUT是片内基准电压输出,通过R3和R4为输入端引入共模偏置电压,可根据需要配置为1.5V或2.5V。该电路可以把50Hz的交流信号直接耦合到AD73360L的模拟输入端。

- 基于C8051F020单片机的多路压力测量仪(01-23)

- 基于FPGA的160路数据采集系统设计(03-22)

- 智能多路信号源的设计与实现(01-10)

- 基于单片机的多路测温仪系统设计(05-09)

- 使用模拟多路复用器的多通道电流测量技术(02-27)

- 用Pico2204A彻底分析视频多路混合器系统的问题(01-12)