基于eRM建立自动化的验证平台

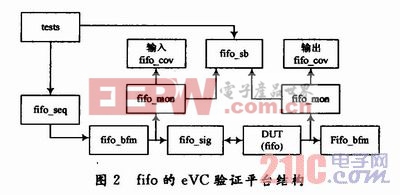

在验证fifo时,先验证fifo的正常读写功能,再验证其读写的极端情况,即将fifo写满直至溢出或者读空,并且实时的监测fifo读出的数据及其状态。图2中的各个文件都是用e验证语言中的Struct或Unit来实现的。

(1)信号接口fifo_signal。fifo_signal中定义了所有需要与fifo相连接的信号,既可以是接口信号也可以是fifo的内部信号,fifo_bfm可以通过这些信号端口向fifo输入激励,也可以采样部分输出信号。

(2)总线驱动接口fifo_bfm。在fifo_bfm中,通过drive()函数将sequence里生成的数据加载入fifo中,也可以在总线端口产生fifo的读写时序,将数据和地址写入fifo中,此组件也可以采样验证人员感兴趣的信号。

(3)输入数据流fifo_seqtlence。在fifo_sequence中,主要是根据所加约束来产生fifo的测试数据。fifo_sequence的定义中包含三部分,分别是item,sequence_driver以及sequence_kind。其中item是模拟fifo需要的输入激励来定义,例如数据以及读写信号等。sequen-ce_driver将生成的数据包发送给fifo_bfm。sequence_kind是指定需要的各种sequence,一般由验证人员根据实际设计协议自主定义的。

(4)监视器fifo_monitor。fifo_monitor主要是对写入和读出fifo的数据进行监测,并实时检查fifo的状态是否与实际的输入相符。fi-fo_monitor是一个被动组件,不能驱动信号,本例中只能采集fifo的数据和状态信号并且释放在Item中定义的事件,作为fifo_coverage统计fifo的数据及其状态覆盖率的敏感事件。

(5)fifo_coverage组件。fifo_coverage中定义了所有的需要统计覆盖率的数据,例如统计fifo的状态变化、写入的数据等,并在每验证完一条测试激励后,可以实时的观测到该覆盖率的变化。

(6)评分板fifo_sb。fifo_sb是一个用来做自动化比较的组件,并对输入的激励进行一系列的处理,预先得到一个绝对正确的输出结果,并与从fifo中fifo_monitor采集到的输出数据逐一进行比较,如果二者的数据或时序不同,就会报出错误信息。

(7)eVC中expect和check检查。在eRM中,提供了一些特定的检查时序的函数和语法,和Verilog中断言Assert一样,使用Expect或者Check可以将fifo的设计规范中的fifo_empty,fifo_full等状态的与实际在仿真器中的监测到的fifo状态进行比较,如果二者不相符,则通过函数dut_error()输出相应的错误信息。

4 结语

本文以fifo为例,采用了基于eRM验证方法学来建立自动化的验证平台,并详细介绍了fifo验证环境框架结构中各个组件的功能和实现方法,极大地提高了fifo的验证效率和功能覆盖率。该平台完全继承eRM验证方法学,主要采用了eRM中的直接测试法和随机测试法,具有较高的验证重用性,大大的缩短了实际项目开发中搭建验证环境的时间,并已得到了广泛的应用。

- 基于Flotherm分析的光伏逆变器的散热设计(05-13)

- Acquired Data Solutions公司使用FlexMotion和LabVIEW为飞机组件测试建立无人测试站(06-14)

- 飞机执行器寿命测试(06-14)

- 智能卡的自动化测试平台设计(05-17)

- 基于数据驱动的自动化测试的研究和实现(06-12)

- 基于指针式电测仪表自动化检定系统设计(01-19)