带有预加重和均衡的高速信号测量

一、高速信号调试面临的挑战

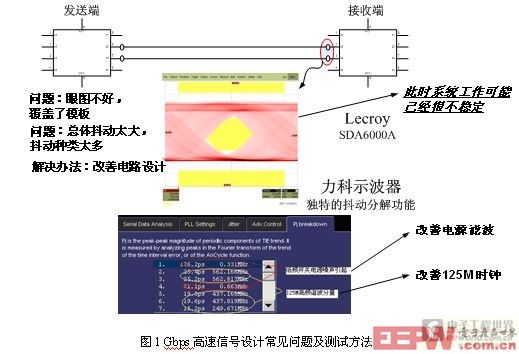

在速率达到Gbps高速设计中,最常见的问题通常会是眼图不好、抖动过大等等。如图1所示,接收端芯片管脚处眼图很差,抖动成分很复杂。对于这样的问题,如果我们使用力科示波器配有的独特的抖动分解功能对抖动进行分解分析可以清楚的看到主要的抖动来自于330khz频点和125MHZ的谐波(如250MHZ、560MHZ左右)的频点,根据这些频点,我们可以更快捷更容易的发现此系统的问题主要可能是因为电源部分和125MZH时钟电路设计得不够完善,这样我们就可以有针对性的去改善这些电路。

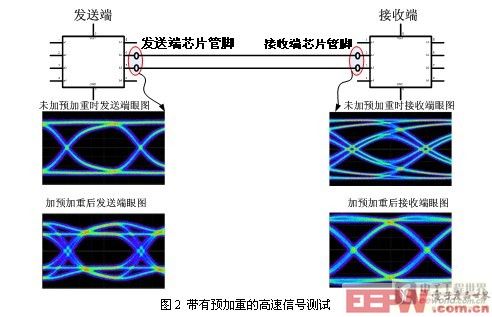

当信号速率进一步提升后,仅改善设计电路可能并不能够完全改善信号眼图,此时发送端芯片一般会具备预加重调节功能,但是需要设计工程师去调节预加重为最优值以确保接收端信号眼图最优化。如图2所示,未加预加重/去加重时候,发送端眼图很好,但是接收端眼图很差;增加预加重后,接收端眼图得到有效的改善。由于芯片厂商一般会提供多种预加重的程度和幅度的调节,所以工程师们通常需要设法选择最优的,一般方法都是通过测试接收端的信号,每调节一次预加重,测试一次接收端信号眼图,需要经过很多次测试对比才能找到最优值,通常效率会比较低。

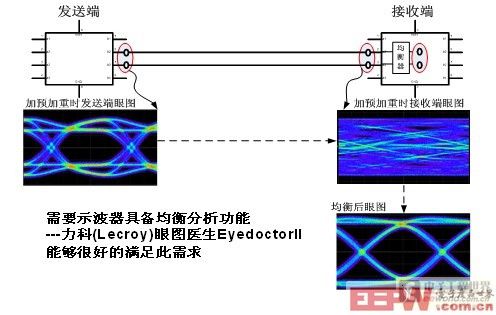

当信号速率更高时,通常达到5Gbps以上时,仅靠调试电路、调节发送端芯片预加重都难以改善接收端信号的眼图,如图3所示,发送端确实已经增加了预加重,但是接收端眼图仍旧闭合了,对于闭合的眼图就无法对其进行分析,而奇怪的是即使眼图如此糟糕,但是系统却仍旧工作良好,那么这是为什么呢——因为芯片接收端采用了均衡技术,虽然在接收端管脚处测得的眼图已经趋于闭合,但是均衡后的眼图通常会得到很好的改善。如图3右侧下方均衡后的眼图已经很好了,但是从图中可看出均衡后的点是在芯片内部,示波器可能不能够直接测试到均衡后的信号,而我们真正需要分析的其实是均衡后的眼图。那么大家应该会问,这样的话示波器在接收端已经测不到均衡后的信号,那么示波器还有什么用呢,在接收端芯片管脚处测试分析信号还有意义吗?力科眼图医生EyedoctorII软件可以为您解决这些问题。

图3 带有预加重和均衡的高速信号测试

二、典型的高速信号设计的主要步骤

由于当前工艺水平越来越高,信号速率高于5Gbps的信号标准已经越来越多,如PCIE2.0达到5Gbps,8Gbps的PCIE3.0标准也可能很快就会推出;USB3.0达到5Gbps,SATAIII达到6Gbps等等。信号速率的进一步提高对电路设计工程师也提出了更多严格的要求;

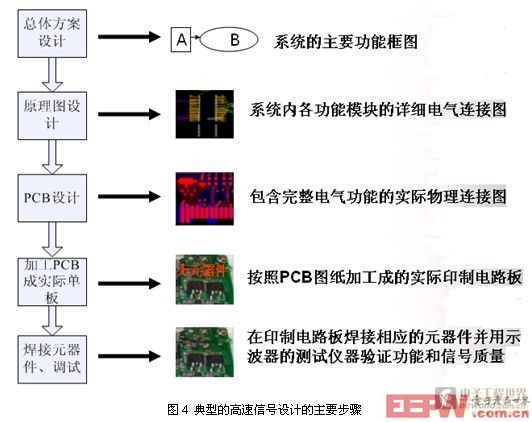

一个典型的硬件系统设计流程大概包括五个步骤:即总体方案设计:主要完成系统的功能框图、原理图设计:主要完成系统内各功能模块的详细电气连接图、PCB设计:主要完成系统内各功能模块的电气连接图、加工PCB版图为尚无元器件的实际单板、最后焊接好元器件进行功能信号等的调试和测试,如图4所示。

在过去低速系统中,通常只在硬件系统设计流程的最后一步进行测试验证来保证达到基本功能要求。而对于高速系统来说,要求会大大不同,第一个不同是需要在设计的更早阶段就要进行信号质量的分析,通常在硬件系统设计流程的第三步即已经完成PCB版图设计但尚未投板之前就进行严格的信号完整性分析;第二个不同是不仅仅是需要满足功能测试的要求,而且是每个高速信号在满足要求之外还需要较大的余量,以确保高速信号乃至整个系统的高可靠性。对于5Gbps以上的信号,还有个不同是有些标准中已经明确提出需要对接收端的进行容限测试,如USB3.0,而以往接收端测试只是选项测试。

三、典型的高速背板系统及其主要设计调试流程

下面我们以一个高速背板系统为例来说明下高速系统的设计流程。如图5所示为一个典型的由两个线卡加上一块高速背板构成的高速信号传输系统。我们看到,图最下方的为带有高速接插件的背板,通过接插件在左右各有两个线卡(line card)插在背板上,左边的线卡上有高速信号发送芯片,右边的线卡上有高速信号接收芯片,如图中红色线所示,高速信号从左边子卡上的发送端芯片发出,经过线卡上的传输线、接插件、背板上的走线、接插件、线卡上的传输线到达芯片接收端。子卡上的高速信号走线通常比较短,对信号的影响很小;背板上的走线都比较长,对信号影响最大,背板面积通常都比较大,生产成本也比较高,所以对于这样一个系统来说,背板设计的成败将至关重要;这样一个系统设计的主要挑战在于如何有效的解决背板传输线对信号质量的影响(如阻抗不连续带来的反射问题、走线过长带来的信号幅度过度衰减问题、高速信号的ISI问题、板间连接处的

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 使用NI PXI和LabVIEW实时模块有效简化硬件在环仿真系统(06-14)

- PCI总线智能GJB289A仿真卡设计(01-06)

- 导入灵活的FPGA验证方法(06-21)

- 测试SDRAM控制器的PDMA(01-04)

- 安捷伦展示3D-EM软件版本整合电路设计流程(05-27)