多通道数据采集系统设计

摘要 介绍了一种基于FPGA+DSP的多路数据采集系统的设计方案,描述了系统的硬件设计方案和硬件电路,阐述了信息采集过程以及外围通讯接口及软件设计。通过Quartus II8.0及CCS 2进行系统仿真,证明了系统设计方案的可行性。

关键词 数据采集系统;FPGA;DSP;FIFO

在以往数据采集系统中,单片机、DSP常被选作主控制器,但随着FPGA性能的不断提高,具有时钟域高、内部延时小、速度快、全部逻辑南硬件完成等优点,因此在高速数据采集方面FPGA有着较大优势,但也存在难于实现复杂算法的缺点。而DSP适合于高速算法的处理,系统采用FPCA+DSP方案,弥补了系统的不足。系统数据采集的控制、缓存及外围通讯部分,用FPCA硬件实现。算法处理由DSP完成。在线采集的数据存放在DSP外挂的SRAM中。

设计采用DE2、THDB-ADA平台进行开发。DE2平台选用FPGA EP2C35F672。THDB-ADA是针对DE2开发板设计的一款子开发板,由FPGA实现对A/D的控制。在系统中只用到了模块的A/D转换部分。其中芯片AD9248是一款双通道模数转换器。另外DSP选用TI推出的TMS320UC5402。

1 系统设计

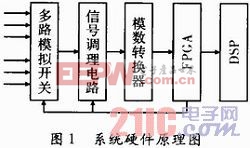

数据采集系统硬件原理如图1所示,由图1知DSP收到上位机发送的命令完成系统工作参数的配置,然后向FPGA发送指令,FPGA收到指令后一是对多路模拟开关进行选通让选通信号通过信号调理电路实现电平调整,并进行A/D转换的时序控制,二是把转换好的数据进行数据缓存,当FIFO满时并产生DSP能识别的外部中断信号及标识信号,通知DSP采集数据,最后DSP对采集到的数据进行滤波处理、变换、谱分析。

2.1 通道切换电路

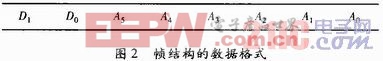

系统采用16通道ADG506模拟开关进行各通道的切换。并具有开关速度快、泄漏小等特点。主要有A0~A3,S1~S8,D,EN端口。其中A0~A3是二进制地址信号输入端,译码结果用于选择有效的输出通道;S1~S16是16路信号的输入端,在此可根据需要选择通道数。D是被选择通道的信号输出端;EN是选择开关使能控制端高电平为有效。FPGA通过数据帧来进行通道选择,每次只选择一路,经A/D转换后送入FIFO。

图中,A0~A5表示所选择通道,其中A4,A5恒为0。D0~D1表示帧结构数据起止标识位。

2.2 信号调理电路

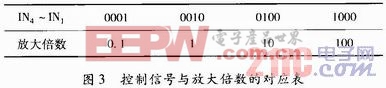

信号调理电路对模拟信号进行一定的放大/衰减,使信号的幅度满足A/D芯片要求。前向调理电路采用高速低噪声的模拟开关MAX4545去选择不同的反馈电阻,同模拟运算放大器MAX817构成标准的反相运算放大器来实现前向调理。MAX817的单位增益3 dB,截止频率高达50 MHz,满足带宽的要求。MAX4545的4根控制线由FPGA设计控制电路去控制,具体是由复位按钮进行边沿触发,使4位输出电平在0001,0010,0100,1000之间轮流切换,将输出电平去控制MAX4545的4根控制线,这就实现了不同的放大倍数之间切换,控制信号与放大倍数的对应关系,如图3所示。

2.3 滤波电路

系统接收到的模拟信号总是混有噪声成分,为达到奈奎斯特采样定理所要求信号的频率范围,需要利用低通滤波器除去干扰信号及抑制混叠现象,即进行衰减与滤除。设计选用二阶巴特沃斯低通滤波电路来滤除信号中的高频分量,其特点是通频带内的响应曲线最大限度平坦,无起伏,而在阻频带逐渐衰减为0.2阶的巴特沃斯低通滤波器幅频。

2.4 FPGA硬件电路设计

FPGA作为接口电路主芯片,充当DSP的前端接口元件,将各种信号转换为DSP能读取的并行格式数据。

FPGA的开发采用自顶向下的设计方法,即指将一个系统按功能划分为不同的模块,而模块再根据需要划分为二级模块,依此直到模块易被实现为止。通过Verilog编程FPGA即可生成双口SRAM模块、ADC接口模块、调理电路放大倍数控制模块、数据接收模块等,以实现对输入信号的采集、存储、处理和输出。

2.5 DSP硬件电路设计

在数据采集过程中,采集的数据缓存在FPGA内部构建的FIFO中在线采集时,通过FPGA与DSP接口将FIFO中的数据转存到DSP外挂的SRAM内,当需要分析数据时再从存储器中取出。DSP外挂Flash存放程序及配置信息。

3 软件设计

3.1 FPGA软件设计

数据在传入FPGA后,直接采用数据在传入FPGA后,可利用SRAM来设计的同步FIFO来缓存采样数据如图4所示:将FIFO抽象为环形数组,并用读或写指针来控制对环形数组的读写。该FIFO提供读使能fiford和写使能fifowr输入控制信号,并指示FIFO的状态非空nempty,非满nfull。未完成一次读写操作地址加1。随着地址的增加,采样数据被依次存入双口SRAM中,当存完数据后向DSP发出信号。

ADC接口模块主要由分频器、通道选择模块及ADC控制模块组成。分频器一方面产牛ADC控制模块的工作时钟,另一方面提

- 多通道频率检测技术的FPGA实现(03-05)

- 多通道隔离示波器在浮动测量中的应用(11-17)

- 高适配度通用化导通绝缘测试仪的设计及应用(10-27)

- 使用模拟多路复用器的多通道电流测量技术(02-27)

- PXI平台实现同步高速多通道数据采集(02-06)

- 关于高速多通道虚拟逻辑分析仪(01-12)