如何利用逻辑分析仪来缩短嵌入式系统的开发时间

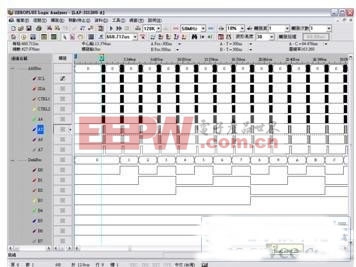

测解读总线(Bus)是非常不明智的选择,而且浪费在此段的量测时间差不多也是占整个研发周期1/4;但是假如工程师用逻辑分析仪来量测解读总线(Bus)时,您知道会有多容易吗?因为逻辑分析仪本身就具有分析总线(Bus)的功能,您只要将要分析的八个I/O(8bits)组合起来成为一总线(Bus) (如图五),还可以专为此总线(Bus)命名,如此工程师在分析总线(Bus)时,就可以很容易的来解读总线(Bus)里的信息(如图六),并且逻辑分析仪还具备进制转换的功能,您只要选择转换后的进制种类,逻辑分析仪就会自动帮您转换,并把转换后的进制值显示出来(如图七),让您不用在浪费时间去做进制的转换计算,如此使用逻辑分析仪量测此案例,将会缩短1/5的研发周期。

图五 R流排分析功能设定

图六 R流排解读显示

图七 进制转换功能设定

触发功能:

说到触发功能,相信工程师们都已经很熟悉了,因为在目前所有的量测仪器当中,几乎99%都拥有此功能,只是大家的触发条件设定不同,假如工程师将触发功能应用的得心应手,那量测仪器所抓取的波形数据将会是使用者最想要分析的那一段,而不会造成让量测仪器抓取一大推的无用数据,进而浪费工程师在Debug的时间。

触发功能是如此的重要,但是示波器的触发功能的条件设定却只有两种边缘触发(上升缘和下降缘),而且只能单一量测通道可以设定触发条件,如此少的触发功能,相信工程师使用起来真的是苦不堪言,因为常常所撷取到的波形数据不是他所想要分析的,进而延长产品的开发时间;但是说到逻辑分析仪之触发功能,其功能之强大,要强过示波器好几千倍,您一定会认为我夸大其辞,但是相信您看完我下面之介绍,一定会改变您的想法,逻辑分析仪除了可以设定触发条件外,还有触发参考电压准位、触发位置、触发次数、触发页、触发延迟各种触发功能之应用,逻辑分析仪之触发条件设定共有六种(如图八),任意信号、高准位、低准位、上升缘、下降缘和任一边缘供工程师所需来设定,而且所有的量测信道均可以做组合触发设定,但需注意要所有触发条件同时成立时(即所有触发通道做AND),才会触发成立,光这一个触发条件设定就已经比示波器还要强大,假如工程师再加入触发位置之选择,可以同时观察触发条件成立之前后的波形数据,或是利用触发次数、触发页和触发延迟可用来分析触发后更后面的波形数据,以解决内存深度的不足,进而可以分析长时间大量的波形数据。

图八 触发条件设定

同时观看模拟和数字信号之方法:

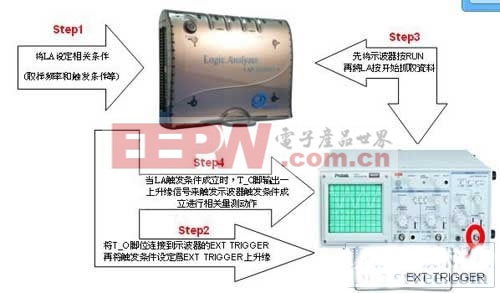

目前市场上很少有产品电路是纯数字或模拟设计,下面介绍利用逻辑分析仪之触发状态输出(Trigger Out)和示波器的外部触发源(EXT Trigger)搭配使用,用以达到在同一时间点可以同时抓取数字和模拟信号;当工程师所设定的触发条件成立时,触发状态输出(Trigger Out)脚位会输出一上升缘波形,所以当工程师想利用此信号输出来触发示波器,只需将此触发状态输出(Trigger Out)脚位连接到示波器的外部触发源(EXT Trigger),并将其触发条件设定为EXT Trigger上升缘,如此使用者只需要执行逻辑分析仪,就可以利用其触发条件成立时,即可以同时触发示波器触发条件成立来进行相关量测动作,其连接方式请看(如图九)。

图九 示波器和逻辑分析仪搭配示意图

结论:

综合前面所述的逻辑分析仪功能,只是它强大功能的冰山一角,所以逻辑分析仪在嵌入式系统的研发过程量测当中,是占有极大的关键地位,但是在目前市场整个产品研发当中,示波器和逻辑分析仪其实是要相辅相成的,如此在产品的研发时间才会更加快速,也才会更加缩短产品的上市时间,进而为公司赚取更大更多的获利,所以工程师必须对示波器和逻辑分析仪这两种量测仪器都要非常的熟悉,要如何运用个别的特性来抓取自己所需的波形数据,如何来搭配相互使用也是一大学问,这些问题都是值得工程师们去深思熟虑!

- 如何利用信道仿真器全面测试LTE系统?(09-12)

- 如何利用7011-S卡测量电容(07-18)

- 如何利用多核PC技术进行图形编程?(02-19)

- 正确选择和使用逻辑分析仪:逻辑分析仪原理(12-01)

- 逻辑分析仪在数字电路测试中的触发选择(04-27)

- 了解逻辑分析仪(05-16)