种OTP存储器片上时序信号产生电路的设计

文中提出了一种片上时序信号产生电路,用于128 Kbit OTP存储器。该时序产生电路由地址变化检测(address transition detection,ATD)电路和脉冲宽度调整电路组成,在芯片内部由ATD电路产生脉冲波形,再由脉冲宽度调整电路产生一个宽度适中的时序信号,该信号即可用于存储器内部时序的控制信号源。例如,将该信号作为控制信号的信号源,可以通过简单的延时、与、或等操作派生出相应的控制信号,这些信号就可用于控制存储器内部各个功能模块,如灵敏放大器,锁存器等。并且该信号源的有效宽度可以很方便的调整,较传统的调宽方式好。

1 电路结构及工作原理

1.1 ATD电路

ATD电路实际上是一种边沿检测电路。ATD电路探测一个信号或者一组信号(比如地址总线)的状态,只要被探测的信号中有一根信号发生的翻转变化,那么ATD电路就会输出一个脉冲。其输出脉冲的宽度由ATD电路的参数决定。由于我们要检测的是地址线的变化,地址线的变化包括从低到高翻转及从高到低翻转,因此需要检测地址线的上升沿和下降沿。

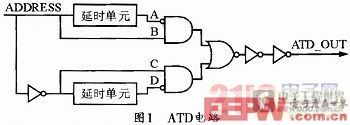

文中所设计的ATD电路能够检测地址线上的两种变化,为双边沿检测电路,电路结构如图1所示。其中ADDRESS端口为地址信号输入,ATD OUT端口为检测电路输出。

若ADDRESS端的地址输入无变化,ATD_OUT输出恒为高电平;

若ADDRESS端的地址输入有变化,无论从0变为1(上升沿),还是从1变为0 (下降沿),由于延时单元的存在,都会使得到达图中的与或非门的输入端A、D的信号比到达输入端B、C的信号滞后延时单元的传播延时时间,从而在经过与或非门之后产生一个低电平脉冲,脉冲宽度由延时单元的传播延时决定。ATD电路的仿真结果如图4所示。从图4中可以看出,在输入ADDRESS端信号的每一个变化的边沿之后,都会产生一个低电平脉冲信号(图4中的ATD_OUT信号)。

1.2 脉冲宽度调整电路

由ATD电路产生的脉冲信号,宽度只有2.5ns,并不能直接用于控制内部电路,因为内部的时序控制信号一般要求特定的有效电平宽度。必须先经过宽度的调整,产生宽度符合要求的信号。

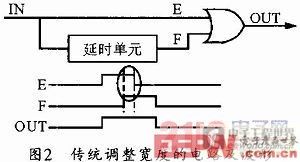

传统的调整宽度的电路一般采用延时来实现,如图2所示。E、F分别为输入波形及经过延时单元以后的波形,OUT为调宽以后的波形,OUT的高电平宽度最大不超过输入信号IN的宽度的两倍,因为E和F必须有交叠的部分(如图中圈起来的部分),否则达不到调宽的目的。这种方式不灵活,假如正好需要两倍输入信号IN的宽度的信号,则不好实现。

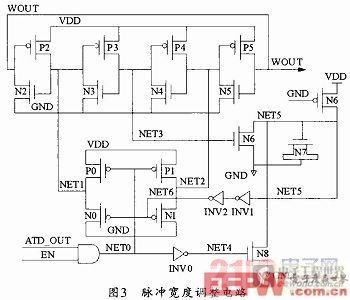

文中设计的脉冲宽度调整电路如图3所示。其中ATD_OUT为ATD电路的低电平脉冲输出信号,EN为使能信号,WOUT为宽度调整以后的脉冲输出信号。 当EN为低电平时,屏蔽ATD_OUT信号,脉冲宽度调整电路不工作;

当EN为高电平,但是ATD_OUT没有低电平脉冲输入(即地址信号没有变化),脉冲宽度调整电路不工作;

当EN为高电平,且ATD_OUT有低电平脉冲输入(即地址信号有变化),脉冲宽度调整电路正常工作。下面介绍其工作原理,N0~N8代表NMOS管、P0~P6代表PMOS管。

第一,EN为高电平且ATD_OUT端口输入低电平脉冲,则NET0上为低电平脉冲信号,低电平到来时先将P0、P1开启,将NET1、NET2拉到VDD,使N2、N4开启,从而将WOUT和NET3拉到GND,迫使N6管关断;同时,NET0上的低电平脉冲经过反相器INV0后使NET4为一个高电平脉冲,迫使N8开启一个高电平脉冲宽度的时间(此处为2.5ns),将NET5拉到GND;因为P6是常开的,只要N6管关断,NET5的电位就会逐渐被抬升,所以增加N8来放电NET5。

第二,低电平脉冲结束以后ATD_OUT变为高电平,此时NET0为高电平,P0、P1关断.NET4为低电平,N8关断,MOS管P6对MOS电容N7及连线NET5上的寄生电容充电,NET5的电位由GND逐渐上升,当NET5上的电位上升到反相器INV1的开关阈值VM以上(设这个过程所需的时间为T,T的大小决定了WOUT的脉冲宽度)时,反相器INV1的输出发生从高到低的翻转,反相器INV2的输出发生低到高的翻转,NET6的电位瞬间被抬高为VDD,迫使N0、N1导通,从而将NET1、NET2从之前的VDD下拉到GND,迫使P3、P5导通,将NET3、WOUT从之前的GND拉回VDD,使N6导通,将NET5清零,准备下一个低电平脉冲的到来;至此,完成了一个完整的调整低电平脉冲宽度的操作。

输出WOUT的脉冲宽度主要由MOS管P6对连线NET5上的寄生电容及MOS电容充电到反相器INV1的开关阈值VM以上的电位需要的时间所决定。

2 充电时间T

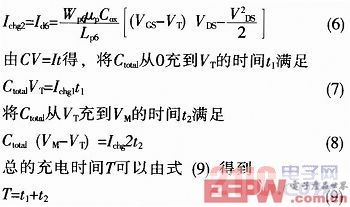

下面推导NET5上的电位从0上升到VM的充电时间T的表达式:

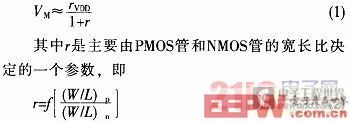

假设反相器INV1的PMOS管和NMOS管的宽长比分别为(W/L)p和(W/L)n,反相器的开关阈值定义为Vin=Vout的点,该点处PMOS、NMOS管均满足VGS=VDS,都处于饱和区,由饱和区电流方程,使PMOS管的电流等于NMOS管的电流,忽略沟道长度调制效应等因素,可以得到

只要知道了PMOS管和NMOS管的宽长比就可以计算出r,进而计算出VM;反过来,如果预先确定了我们需要的VM的值,可以由(1)、(2)两式算出反相器PMOS管和NMOS管的尺寸。例如,我们需要一个对称的反相器INV1,则希望VM的值正好是VDD/2,由(1)式可得r的值约为1。

假设N7管的宽长比为Wn7/Ln7,栅氧单位面积的电容为Cox=εox/tox,N7的栅源、栅漏覆盖电容之和为2CoxxdWn7,其中xd是由工艺决定的参数,为忽略N7的栅电压VGS(即NET5上的电压)对其栅电容的影响,得到N7的栅电容Cg7为

假设反相器INV1的栅电容为CgINV1,CgINV1的值可以由上面的方法带入反相器的尺寸计算得到。

假设N6管的漏极结电容为CjN6,CjN6的值可以由N6管版图实现时的漏结面积与工艺的单位面积结电容参数计算得到。

连线NET5上的总的寄生电容Ctotal为

假设P6的宽长比为Wp6/Lp6,阈值电压为VT,NET5上的电位由于P6的充电从0开始逐渐往上抬升。

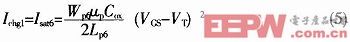

当NET5的电位VNET5满足VNET5≤|VT|时,P6工作在饱和区,充电电流Ichg1即是P6的饱和区电流

当NET5的电位VNET5满足|VT|VNET5≤VM时,P6工作在线性区,充电电流Ichg2即是P6的线性区电流

通过调节N7、P6的尺寸可以分别调整电容或者充电电流的大小,达到调整时间T的目的,而时间T的大小直接表现在电路的输出WOUT的脉冲宽度上;即通过调整N7、P6可以达到控制输出WOUT的脉冲宽度的作用。不管需要什么样脉宽的WOUT,都能通过控制N7、P6来实现。

一次可编程 片上时序 地址变化探测 脉冲宽度调整 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)