基于CPLD的多路温度采集系统电路及设计方案

摘要 应用温度采集芯片MAX6675,将其与K型热电偶结合,利用CPLD对其进行控制,实现一个多路温度采集系统。文中介绍了系统的硬件电路结构,并根据芯片的内部时序介绍了CPLD内部逻辑电路的设计。通过两种温度环境下的系统测试,给出了温度数据的统计图,证明了MAX6675及设计的多路温度采集系统的良好性能。

K型热电偶是当前工业生产、科学实验较为常用的一种温度传感器,它可以直接测量各种生产中0~1 300℃范围内的液体蒸汽,气体介质和固体表面温度。由于它的测量范围及其较高的性价比,使得K型热电偶应用广泛。然而K型热电偶存在非线性、冷补偿等问题,特别是在处理补偿问题时,需要付出较高的代价且难以有较好的成效。所以本文介绍的MAX6675温度采集芯片,弥补了K型热电偶上述缺陷。将MAX6675和K型热电偶结合并用于工业生产和实验,能为工程带来诸多便利且减少繁琐的附加电路。本文给出了基于CPLD的多路温度采集系统电路、内部逻辑设计模块、误差分析和实验统计报告,以及MAX6675多路温度采集系统的应用过程和性能报告。

1 MAX6675介绍

MAX6675是美国Maxim公司生产的带有冷端补偿、线性校正、热电偶断线检测的串行K型热电偶模数转换器,它的温度分辨能力为0.25 ℃;冷端补偿范围为-20~+80℃;工作电压为3.0~5.5 V。

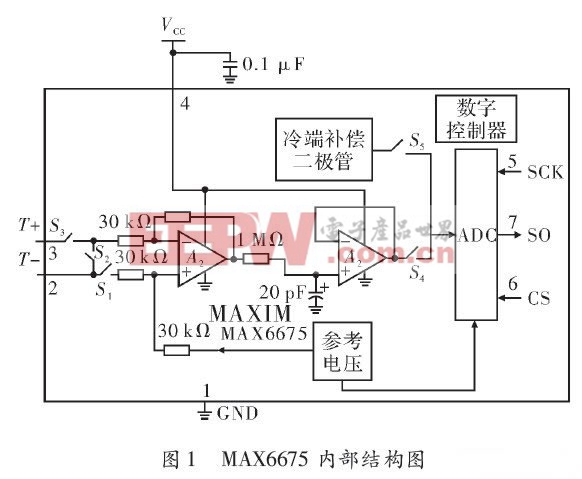

根据热电偶测温原理,热电偶的输出热电势不仅与测量端的温度有关,而且与冷端的温度有关。在以往的应用中,有多种冷端补偿方法,如冷端冰点法或电桥补偿法等,但调试较复杂。另外,由于热电偶的非线性,以往是采用微处理器表格法或线性电路等方法,来减小热电偶本身非线性带来的测量误差,但这些增加了程序编制及调试电路的难度。而MAX6675对其内部元器件的参数进行了激光修正,从而对热电偶的非线性进行了内部修正。同时,MAX6675内部集成的冷端补偿电路、非线性校正电路、断线检测电路都给K型热电偶的使用带来了便利。 MAX6675的特点有:(1)内部集成有冷端补偿电路;(2)带有简单的3位串行接口;(3)可将温度信号转换成12位数字量,温度分辨率达0.25℃;(4)内含热电偶断线检测电路。其内部原理图如图1所示。

2 系统构架

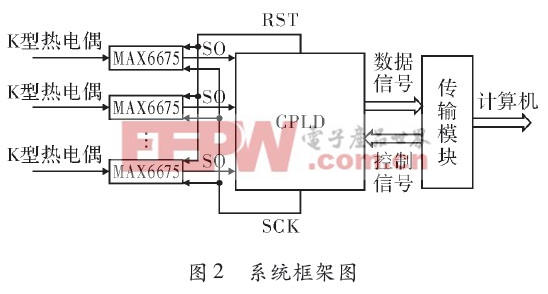

系统框架如图2所示,该系统以CPLD为核心,由多路K型热电偶和MAX6675将外界温度模拟信号采集并转换成数字信号,并将数据传入CPLD进行相应的处理,然后通过通信模块将数据传送给计算机,最后用计算机做数据统计及处理。系统中的通信模块可以根据工程或实验环境的不同使用不同通信方法,如串口通信、PCI传输卡等。由于工程应用的原因,本文使用PCI传输卡作为数据传输方式。

3 CPLD内部逻辑

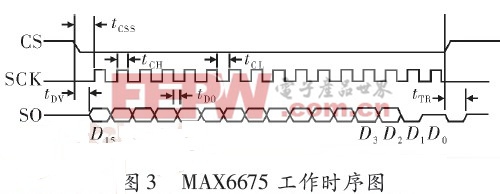

如图2所示,K型热电偶将采集的模拟信号传送给MAX6675,再由它转化成数字信号传入CPLD,CPLD根据MAX6675芯片的时序进行数据处理得到需要的信号,最后由传输模块传到计算机进行数据显示和统计、处理。所以本文的重点工作便在CPLD内部逻辑的设计。在进行内部逻辑设计之前,须了解MAX6675的工作时序与原理:当CS引脚由高电平变为低电平时,MAX6675停止任何信号的转换,并在时钟SCK的作用下向外输出已转换的数据;当CS引脚从低电平变到高电平时,MAX6675将进行下一轮数据的转换。一个完整的数据读取需要16个时钟周期,数据的读取在SCK的下降沿进行。MAX6675的工作时序图如图3所示。

如图3所示,根据芯片手册tcss是CS下降到SCK上升的时间,规定其最小值为100 ns,tCH+tCL为SCK的一个时钟周期,规定最小周期为200 ns,tDV为CS下降沿到数据输出的时间,规定最大不超过100 ns。tDO为SCK下降到输出有效数据的时间,tTR为CS上升沿到数据停止输出地时间,规定最大值均为100 ns。根据这些手册上的这些时间规定,在设计CPLD内部逻辑电路时便严格按照要求,将SCK时钟周期设为1 000 ns即1 MHz,tcss设为1 000 ns,tDVtTR都设为100ns。图中还可以看出SO是16位的输出数据,其中只有D14~D3位为温度数据,D15位为无用位,D2位为热电偶断线测试位,D1位为MAX6675标识符,D0位为三态,所以从16位数据中取出D14~D3这12位数据进行转换和处理。基于以上分析,设计了如图4所示的内部逻辑模块。

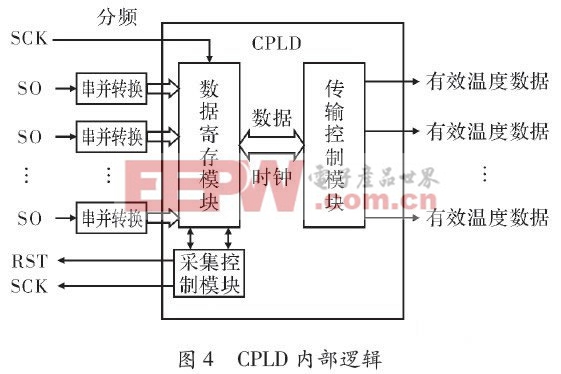

CPLD内部逻辑如图4所示,为了将12位有效数据提取出来,先要将串行的SO输入信号转换成并行的,利于有效数据的提龋图中的CLK是指总时钟,用一个40 MHz的晶振,通过分频为芯片提供时钟。根据芯片数据手册和上述分析,给SCK信号1 MHz频率。以芯片时序要求,给RST信号2.5 Hz时钟,即0.4 s完成一次数据采集和数据传输。图中数据寄存模块的功能是为了寄存各路并行输入信号,便于后期上传。采

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于CPLD和89S51的多功能信号测量仪(10-04)

- 基于MCU+CPLD的相位差和频率的测量方法研究及实现(01-16)

- 基于单片机和CPLD的数字频率计的设计(01-27)

- 脉冲信号源的CPLD实现方法(02-27)

- CPLD 在线缆快速测试技术中的应用(03-01)