采用TMS320VC5509A 图像采集处理系统设计方案

摘要: 传统图像采集处理系统多以计算机为平台, 其图像处理速度不高, 且体积庞大、功耗大。为克服这些缺点, 介绍了一种成本低、结构简单、体积小、功耗低的图像采集处理系统。以TI 公司的T MS320VC5509A 为核心器件, 采用大容量FIFO 完成视频数据存储, 利用CPLD 完成逻辑控制功能。软件采用C 语言对5509A 进行编程, 完成整个采集过程的系统调度工作及图像处理算法, 增强了易读性和可移植性, 提高了图像处理的速度。

0 引 言

随着现代电子技术的发展, 图像采集和处理技术在工业、医学、军事等很多领域得到了广泛的应用。DSP( digital signal processor ) 芯片, 也称数字信号处理器, 有很高的集成度, 是一种特别适合于进行数字信号处理运算的微处理器器件, 它以其独特的哈佛结构和流水线技术以及快速实现各种数字信号处理算法的特点广泛应用于图像处理、语音合成等领域。T I 公司推出的高性能、超低功耗和低价位的定点数字信号处理器TMS320VC5509A, 具有体积小、处理速度快、使用灵活方便等特点。基于DSP 的图像采集处理系统能较好地满足处理数据量大、小型化便携式、高速传输以及大容量存储空间的需求。

1 TMS320VC5509A 简介

作为本系统的核心器件, 5509A 内核工作频率可达到144 MHz( 6. 94 ns) , 内核供电为1. 6 V。由3 部分组成:中央处理单元( CPU) 、内部存储器和片内外设。

CPU 内部总线由一条读指令数据总线( 32 位) , 1 条读指令地址总线( 24 位) , 3 条读数据数据总线( 16 位) , 3 条读数据地址总线( 24 位) , 2 条写数据数据总线( 16 位) , 2 条写数据地址总线( 24 位) 组成。CPU 提供2 个MAC 单元支持乘加运算, 每个MAC 可以完成一次17 位× 17 位的乘法和一次40 位的加法操作, 结果送入累加器。采用2 段分离的流水线: 第一段为指令流水线; 第二段为执行流水线。

5509A 内部有一个时钟发生器, 为了减少功耗, 时钟发生器和其他很多模块一样具有空闲( IDEL) 模式。5509A 支持2类外部存储器接口, 即异步接口和同步接口。

2 系统硬件结构及原理

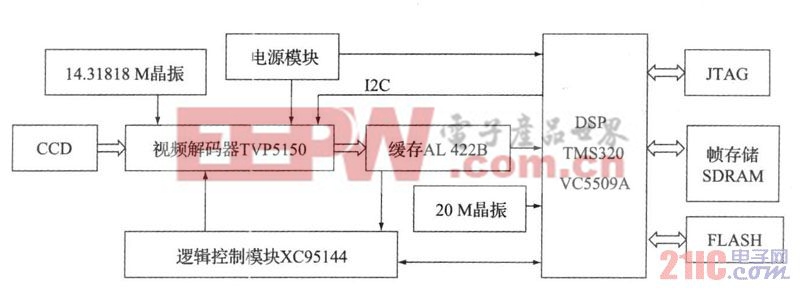

硬件系统总体结构框图如图1 所示。本系统主要包括两个子系统: 图像采集系统与图像处理系统。图像采集系统包括CCD 摄像头、视频采集芯片、缓存以及用于逻辑控制与地址译码的CPLD; 图像处理系统则包括DSP、外扩的FLASH 和SDRAM。主要工作流程为: 由CCD 摄像头摄取视频图像, 输出标准PAL 制视频信号; 视频解码器将模拟视频信号转换为标准的数字视频信号并送入缓存, 缓存暂存视频数据; 待图像采集完毕后, DSP 通过外部存储器接口从缓存中读取图像数据并存入帧存储器, 以供后续处理。逻辑控制模块完成各部分之间的接口逻辑匹配和控制逻辑。电源模块为系统各部分提供电源。

图1 硬件电路总体结构

2. 1 图像采集模块

2. 1. 1 T VP5150 与AL422B 的接口实现

由于本系统中从TV P5150 输出的数字视频码流是由AL422B 缓冲的, 故需要将5150 的输出端口与A L422B 的写入端口相连。5150 的数据总线除了要与A L422B 的数据总线相连, 同时5150 还需要为AL422B 提供写时钟WCK, 写指针复位信号/ WRST 以及写使能信号/WE。

TV P5150 有两种标准输出格式8 位ITU??R BT. 656 格式的数字信号和8 位YU V4: 2: 2 的数字信号。在本系统中采用后一种输出格式( 通过I2C 配置5150 芯片) , 数据总线宽度是8 位。

2. 1. 2 TMS320VC5509A 与AL422B 接口实现

当缓存中的数据存满后, 5509A 需要读取FIFO 里的数据, 因此要连接5509A 的EMIF 接口与AL422B 的读数据端口。5509A 的EMIF 接口可以连接各种异步或同步存储器, 根据EMIF 接口的特性, 本系统采用异步接口模式。5509A 的数据总线需与AL422B 的数据总线相连的同时, 要向A L422B 提供读使能信号/ RE、读时钟信号RCK 以及输出使能信号/ OE。将AL422B 的数据输出,通过EMIF 将数据传输至SDRAM。AL422B 外扩在/CE2 这个空间, 当/ CE2 和/ AOE 都为低电平时, 则使AL422B 的输出使能/OE 有效, 但是要等到/ ARE 变为低电平的时候, 才能使读使能/RE 有效, DSP 开始读取AL422B 中的数据。5509A 与FIF0 接口图如图2 所示。

图2 5509A 与FIFO 接口

对于5509A 与A L422B 的接口, 有以下逻辑关系:

RCK = CLK OUT ( 1)OE = CE2+ AOE ( 2)RE = CE2+ ARE ( 3)式中: RCK 为FIFO 的读时钟信号引脚; CLKOUT 为DSP 输出时钟; / OE 为FIFO 的输出使能信号; / AOE 为EMIF 接口的输出使能信号; /RE 为FIFO 的读使能信号; / ARE 为EMIF 接口的读使能信号。

2. 2 图像处理模块

2. 2. 1 TMS320

- 基于TMS320VC5509A 的图像采集处理系统(08-01)

- 基于TMS320C6713B的实时数字视频消旋系统设计 (10-15)

- 8051、ARM和DSP指令周期的测试与分析(04-19)

- 基于DSP2812的带式输送机多路温度检测系统设计(06-18)

- USB接口多路高速数据采集系统在LABVIEW平台的设计(11-08)