高功放高压联锁电路改进与测试

摘要:高压联锁性能的好坏直接影响设备能否正常工作。通过分析CPI高功放(HPA)的延时加高压程序、高压联锁电路和交流延时器工作原理,研究出一种新改进的高压联锁电路方案和用于交流延时器的测试方法。分析阐述表明,该方案和测试方法克服了CPI高功放的高压联锁方案的弊端。另外,根据分析结果设计了延时测试电路,它可对交流延时器性能参数进行定量测试。

关键词:CPI;高功放;高压联锁;交流延时器

微波统一测控系统的高功放(HPA)高压电源及控制保护电路是设备稳定可靠运行的重要保证,关于这方面国内已经开展了一定的研究。高功放交流延时器用于二次加高压,其性能好坏直接影响设备能否正常工作。某船载高功放设备曾出现过两次延时器损坏事件,严重影响了试验任务的顺利执行。本文通过分析高压联锁电路和该延时器的工作机理,提出了一种高压联锁电路的改进方案,专门用于解决延时器频繁损坏的问题;提出延时器测试方案,并设计出专门用于延时器性能测试的测试电路,该电路已经在实际工作中得到了应用和验证。

1 高功放延时加高压程序分析

为了降低瞬时加高压引起的浪涌电流,一般的高压设备都采用了防浪涌电流电路。某船载高功放设备采用二次加电的方法来降低浪涌电流。图1和图2为HPA加高压原理和防浪涌电路原理。

高功放微机对各种限制条件进行判决,送出高压允许(HV ENABLE,直流+15 V)控制信号;信号控制送给高压继电器的射束通(BEAM ON CMD,~115 V),使高压继电器吸合,送出步进入STEP START IN(~115 V)信号,此信号进入延时加高压电路,使K1吸合,~380 V通过分压电阻部分加到高压变压器上。经过K3适当延时(0.1~0.7 s)后,使K2吸合,降分压电阻旁路,使~380 V全部加到高压变压器上,并送出步进结束(STEP START COMPLETE)信号到高功放微机,通知延时结束,再由调压单元调整补偿高压至所设高压(调压单元还有阻止输出直流电压的上下浮动的功能)。

2 CPI高功放高压联锁电路分析及改进

2.1 CPI交流延时器

2.1.1 交流延时器工作原理

交流电刚到延时器时双向可控硅处于断开状态,整流电路工作,整流出的直流电压加到延时控制单元上。当由R延时和C延时组成延时电路延时到时,控制程控定时器送出控制信号给双向可控硅(晶闸管),使其导通,将整流电路正负输出端短路。此时从延时器输入端观察,整流电路输入阻抗很小,近似短路,交流电直接通过整流电路。此后整流电路没有直流电压输出,延时控制单元停止工作。根据双向可控硅导通特性,在其导通后只要通态电流大于维持电流,即使触发信号消失,它仍处于导通状态。延时器将一直处于导通状态。

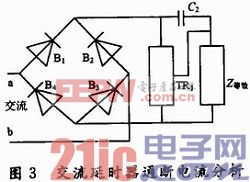

图3为该交流延时器通断时的电流分析。TR1为双向可控硅,Z等效是从双向可控硅右面向右观察的等效阻抗,其模值很大。

当双向可控硅处于断开状态时,a、b两点间向右看观察的阻抗也很大,延时器处于断开状态。延时器断开时间内,假设在某一时刻,a点电压高于b点电压,那么电流从a点流经B1、Z等效以及B3到b点。由于Z等效很小,可以认为a点和b点之间是处于断开状态,电流很小,即延时器处于断路状态,整流器对交流进行整流。适当延时后,双向可控硅被控导通,双向可控硅将Z等效旁路,若a点电压然高于b点电压,则电流从a点流经B1、双向可控硅以及B3到b点。由于双向可控硅导通时阻抗很小,则认为a点和b点之间是处于导通状态,即延时器处于导通状态,整流器没有整流作用。

2.1.2 交流延时器性能参数

型号为49MD06FA的交流延时器其性能参数如下:

(1)加在两端电压:~120 V。

(2)延时时间:0.1~0.7 s可调。

2.2 CPI高压联锁电路设计方案局限性

CPI对船载系统高功放原理图进行了改进。具体改进部分如图2中的加粗虚线部分所示。在K1前加了一个常开点B,在K3两端加了一个常闭点A,它们均由K2控制。STEP START IN到来后,K2的常闭点使K1吸合,K3延时结束使K2吸合,K2控制常开点B接通而将K3旁路,常闭点A断开而将K1断路。这样,在加高压结束后,K1和K3都停止工作,延长了它们的使用寿命。

但这种设计存在一定的局限性,主要是由于用同一个器件K2来控制A点和B点。第一,K2提供不了这么多触点,它只有一个常开点和一个常闭点;第二,即使K2能提供这两个控制点,用同一个接触器K2控制要考虑通断的时序问题。这里的常开点和常闭点是机械关联的,即先断开常闭点A后才能闭合常开点B,就存在一个时间差△t,而机械关联不可能使△t足够小,以至于K2还没来得及断开,常开点B又使K2吸合而保持高压接通。这在逻辑上也是一个错误。

2.3 高压联锁电路改进方案

因此,新改高功放没有按图纸改进,仍然采用原来的高压联锁电路。要使CPI设计方案得以实施,必须对电路进行改进,先让B闭合,然后才能将A断开。

为此,提出两种改进方案。

第一种,把常开点B和常闭点A用机械开关代替。该方案简单,但是自动化程度低,并且加高压和去高压都必须按严格的步骤操作,否则可能损坏设备。即加高压前要先把A接通、B断开,加高压完成后要将A断开、B闭合以保护K1和K3。去高压后要将A接通、B断开,为下一次加高压做好准备,防止不小心损坏设备。

第二种,采用两个小功率的耐压超过~120V的直流继电器。当加高压完成时,由K2控制J1,J1将B闭合而旁路K3,形成STEP START COMPL ETE信号送给高功放微机;同时控制J2,J2通电吸合后使A断开,K1停止工作。该电路结构简单,制作成本低廉,时序逻辑合理,充分利用就近的线路和信号,可以更大限度地缩短K1和K2的工作时间,完全实现了CPI最初的改进设想。该改进方案最大的优点是用廉价且易于采购的器件来保护价格昂贵、难于采购的器件,可以大大降低经济开支,缩短设备维护过程。

两种方案相比,第二种有明显的优势。它不但操作过程简单,而且自动化程度很高,避免了第一种方案中操作不慎可能损坏设备的弊端,是优先考虑的选择方案。

3 延时器测试电路设计及应用

高功放延时器的验证基本方法是将其安装到高功放上,加高压进行试验,观察高压是否能加上,检查其延时功能。该验证方法不但不可靠,而且可能会对高功放其他部件造成损害,引发其他并发故障。一旦出现其他并发故障,故障部位难以定位,故障机理难以分析。针对这种情况,设计了一种测试电路。该电路经济可行,可以定性和定量地检查测量延时器的性能和指标。

3.1 电路构成及测试原理

图4为自制交流延时器测试电路。该电路的供电由一可调变压器提供~120 V,用开关K代替K1控制给K3的供电,用三个电阻和灯泡作负载代替K2,插座上可插上被测延时器K3,用一个电容引出测试点,用记忆示波器测量延时时间。灯泡还可作通断指示,辅助判断延时器是否具有延时导通的作用。

- 速调管高功放的维护分析及故障处理(03-17)

- 集成电路的电磁兼容测试(06-06)

- 低功耗制造测试的设计-第一部分(01-29)

- 低功耗制造性测试的设计-第二部分(01-29)

- ASA测试技术在电路维修测试仪上的应用(06-28)

- 示波器前级衰减电路(06-21)