DDS技术在高频石英晶体测试系统中的应用

AD9912的外围电路主要由5大模块组成:电源、时钟源、SPI通信接口、启动配置逻辑、输出信号处理电路。

AD9912的电源分为模拟3.3 V、数字3.3 V、模拟1.8 V和数字1.8 V四大类。模拟3.3 V和数字3.3 V经过滤波器互相隔离。模拟1.8 V和数字1.8 V经过滤波器互相隔离。AD9912的参考时钟选用25 MHz的高性能恒温石英晶体,AD9912内部的PLL电路对该参考时钟进行40倍倍频得到1 000 MHz时钟信号作为AD9912的系统时钟。32管脚CLKMODESEL为时钟模式选择管脚,如果使用石英晶体作为系统时钟输入,该管脚应该接地,如果使用振荡器或者外部时钟源作为系统时钟输入,该管脚应被上拉至1.8 V。由于选用的是石英晶体,该管脚接地。

SPI通信接口硬件连接如图6所示。

启动配置逻辑包含S1,S2,S3,S4四个管脚。其中S4为逻辑0时,选择时钟模式:使用石英晶体作为系统时钟输入,并且由AD9912内部的PLL电路进行倍频得到时钟信号;S4为逻辑1时,选择时钟模式:由外部直接输入时钟信号。因此,把S4设置为逻辑0。S1、S2和S3的8种不同逻辑组合,用来选择8组预置的16位频率控制字。允许在未配置I/O寄存器的情况下,产生8种频率不同的信号。由于本测试系统需要的是扫描信号,不需要某固定频率的信号,因此,把S1,S2和S3设置为逻辑0,使DDS在启动时不输出信号。

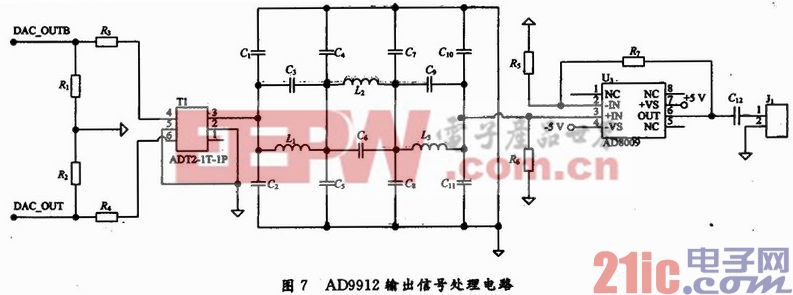

AD9912的输出信号为差分信号,采用射频变压器将差分信号转换为单端信号,并经过低通滤波电路和功率放大电路后输入至π网络和补偿网络。AD9912输出信号处理电路如图7所示。其中,DAC_OUT和DAC_OUTB是AD9912输出的差分信号。

2.3 信号源软件设计

处理器STM32F103控制AD9912输出频率信号,主要是通过SPI向AD9912的寄存器中写入对应的值。

由于选用25 MHz的高性能恒温石英晶体作为参考时钟,需要使能系统时钟PLL,应将寄存器0x0010的第4位设置为逻辑0。

寄存器0x01A0~0x01AD为输出信号控制字,其中0x01A0~0x01A5为保留寄存器,0x01A6~0x01AB为频率控制字,0x01AC~0x01AD为相位控制字。

输出信号频率与频率控制字关系为:

fDDS=(FTW/248)fs (1)

式中:fDDS为AD9912输出信号频率;FTW为频率控制字;fs为AD9912的系统时钟频率。

由式(1)得到:

FTW=round[248(fDDS/fs)] (2)

例如,当fs=1 GHz,fDDS=19.44 MHz,则FTW=5 471 873 547 255(即0x04FA05143BF7)。

输出信号相位与相位控制字关系为:

△φ=2П(△phase/214) (3)

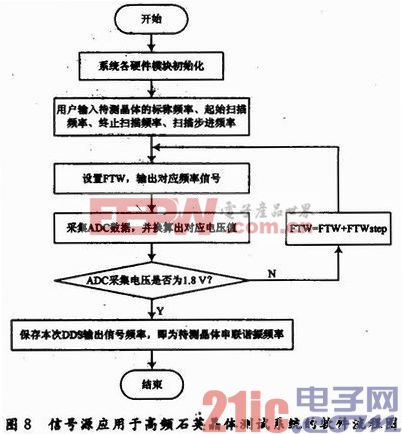

式中:△φ为AD9912输出信号相位;△phase为相位控制字。由于信号源需要应用于高频石英晶体测试系统中,所以,不能只输出一个固定频率的信号,必须输出扫频信号。测试之前,通过健盘或触摸屏输入待测晶体的标称频率、起始扫描频率、终止扫描频率、扫描步进频率,处理器根据式(2)算法,由扫描步进频率计算出扫描步进控制字(以下称为FTWstep)。图8所示为信号源应用于高频石英晶体测试系统的软件流程图。

信号源的精度和稳定度直接影响到测试系统测量石英晶体频率的精度和稳定度。因此,使用CNT-90型频率计测量本系统信号源输出的信号频率。实验结果表明,信号源输出信号频率的精度高于±0.1 ppm,频率的稳定度高于±0.1ppm,实验数据如表1所示。

表中,f为设定的频率值;f为实际测量的频率平均值;△f/f为相对偏差。

4 结语

本设计成功地把DDS技术应用到高频石英晶体测试系统中。实现了基于DDS技术的宽带信号源。该信号源具有输出频率范围宽、精度高、稳定度高、频率分辨率高,频率切换速度快的特点,从而满足了高频石英晶体测试系统对信号源的要求。

- DDS函数信号发生器的优点(09-28)

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于AD9858的线性调频源设计(11-03)

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)