自适应均衡器系统电子电路剖析

自适应电缆均衡器是串行数字视频(SDV)广播和串行电信设备接收器前端的基本组成部分,它们还可以用于其它类型的有线通信系统。均衡器直接与传输线接口,恢复由电缆造成信号幅度及带宽的损耗。由于均衡器直接连接到电缆,因此它很容易受ESD、EMI/RFI和器件所产生的噪声影响,均衡器的工作特性也倾向于增大设计中噪声的影响。一个采用抗干扰自适应电缆均衡器的鲁棒系统也必须保持均衡器的一些良好工作特性,如宽输入动态范围、宽信号带宽、低残留输出噪声、高输入回波损耗,以及最大均衡电缆长度等。

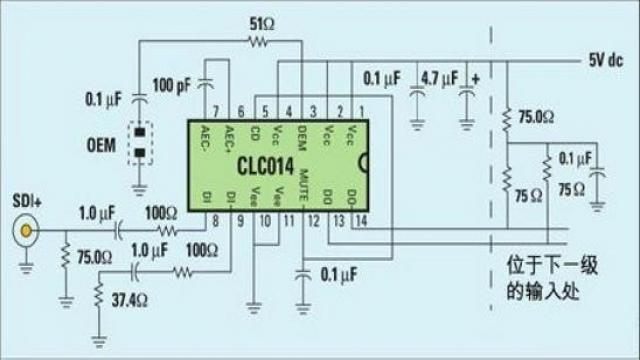

图1 :均衡器电路图

ESD、EMI/RFI和器件产生的噪声是有线通信系统中的三大主要干扰模式:ESD可以毁坏或摧毁电路内外的有源及无源器件;EMI/RFI会影响系统的信号处理,严重时会造成系统基本功能的失效;器件产生的噪声可以影响电路的工作,降低其性能,亦可导致系统失效。

自适应均衡器设计的技术挑战

要设计一个能应对以上干扰的鲁棒系统是一个不小的挑战。自适应电缆均衡器并非简单的数字器件,这是设计者都必须仔细考虑的基本事实。美国国家半导体的 CLC014、CLC012和最新的CLC034自适应均衡器是高性能的模拟器件,它们是高增益、高带宽、模拟、射频、AGC放大器滤波器。在正确集成情 况下,它们能与其它所有系统元件(包括机箱、无源元件和PCB等)共同抵御内、外部的干扰。一般情况下,当电缆长度为最大时,均衡器接收到的信号为最小。 所以,均衡器的增益与带宽要在最大值。但当输入端未连接,没有外接信号时,增益与带宽也是最大。在最大增益情况下,即使少量的有害EMI或传导干扰都会被 大大地放大,影响均衡器的正常工作。好的PCB设计可以阻止干扰,避免一些常见的均衡器应用故障,如:无法在给定数据速率下均衡最大电缆长度;电缆长度小于最大值出现数据错误;当输入端开路时有虚假的或随机输出数据;信号检测错误指示。

这些故障是由以下原因引起的:源于系统机箱内部或PCB上的EMI辐射;逻辑器件或电源通过输入网络的元器件安装管脚耦合到输入端的噪声;其它附近电路 对输入端及/或自适应均衡器电路(AEC)的串扰;均衡器输入、输出电路的耦合。ESD事件会严重损坏半导体器件,特别是当这些器件没有导电包装材料保护 时,更容易遭受损害,即使半导体器件安装在电路上也会被损坏。用于直接电缆接口的器件,如线路驱动器和电缆均衡器等都按照最大ESD额定电压而设计。即便 如此,只依赖于半导体器件本身来提供所有ESD防护,而无视其额定ESD防护值的高低,仍是不明智的做法。均衡器输入电路有通过终结电阻接地的低阻抗路径 优点,提高了对ESD的耐受能力。输入电路中使用的元器件都应当有足够的ESD抵御能力,以应对设计中的最大ESD事件。通过适当的选择与设计,所有的电 路元器件(包括机箱、连接器和PCB等)均可以实现均衡器和其它接口器件的ESD防护。

提高性能的设计方法

以下这些设计措施可以抵御电子干扰,提高均衡器整体工作性能:

1.将均衡器输入网络及AEC电路与外部、卡上的高电平信号隔离或屏蔽开;

2.采用耐用的 输入电路元器件,抑制ESD事件;

3.采用多层PCB,用独立的传输线和电源-地层,实现隔离、屏蔽和ESD防护;

4.在电源、地层间采用薄的电介质 (6mil以下),以提高层间电容和高频衰减;

5.旁路电容、终结电阻、集电极负载电阻以及VCC和VEE管脚焊盘与层面连接时采用两个过孔;

6.不要将 多根VCC和VEE管脚连接到一个过孔,因为这可能引起器件中的噪声。

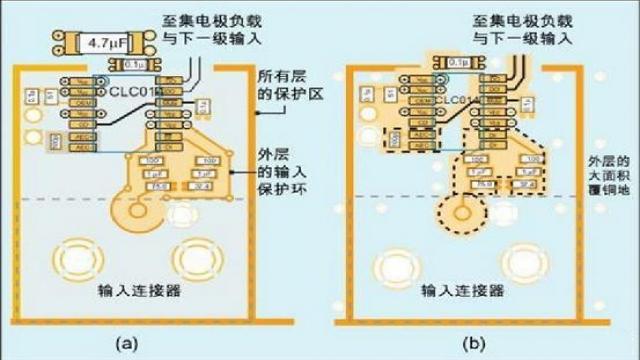

图2a:输入电路保护。 2b:用覆铜做屏蔽

图1所示是推荐的CLC014均衡器电路,图2是相应的PCB布局。在PCB板上,采用了一些将均衡器电路与有害信号干扰隔离开来的措施。在输入网络和 AEC电容下方的电源层去除了铜箔,消除了电源层噪声向输入电路和AEC电路耦合的路径。所有层都除去了部分铜箔(深色阴影线),以隔离均衡器的电路。这 些隔离带可以防止邻近电路通过中间层与均衡器电路的直接接触。这样,干扰信号要接近输入电路就必须沿隔离带走一个较长的路径。

这样的做 法增加了低通滤波效果,提高了对有害信号的衰减能力。用于提供信号环路(loop-ba

- 均衡器如何解决差分对中插损的问题(10-12)

- 基于神经网络的微波均衡器建模与仿真(05-13)

- 无线通讯的噪声干扰与验证要点(07-11)

- 通过改变电源开关频率来降低EMI干扰(05-05)

- 无线基站接收通道混频器的设计选择(07-05)

- 基站射频卡时钟树设计问题(05-03)