CY8C29666芯片的高精度频率测量系统设计

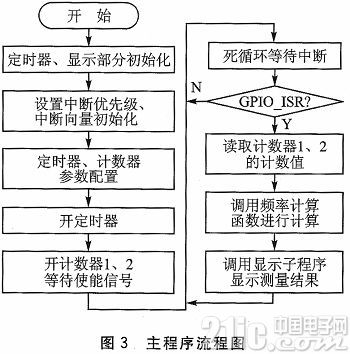

由主程序、中断服务子程序和显示子程序构成。为了使设计出来的软件功能明确,便于调试、扩展和移植,采用结构化的程序设计方法。主程序如图3所示。

需要注意的是,定时器最终计数结束后的下一个系统时钟周期,定时器会自动重新加载计数初值,所以要在此之前读取两计数器的计数值。故使用定时器的最终计数输出功能,在此时输出一个脉冲触发中断,即可通过编写中断处理程序实现读取计数值,并重置计数器初值的功能。

3 实验结果及误差分析

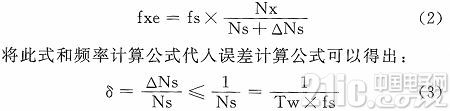

设标准信号的频率为fs,通过配置定时器模块得到的闸门时间为T,被测信号频率的理论值为fxe,T时间内计数器对被测频率信号和基准频率信号的计数值分别为Nx和Ns,则被测信号的频率为fx=fs×Nx/Ns。在忽略基准频率fs误差的情况下,测频可能产生的误差为:

δ=[(fxe-fx)/fxe]×100% (1)

由于测量中两计数器的计数启停都由fx的上升沿触发,即实际闸门时间为被测频率信号的整数倍,故对fx计数不存在误差;对fs的计数Ns最多相差一个脉冲的误差,即|△ Ns| ≤1,此时测量频率为:

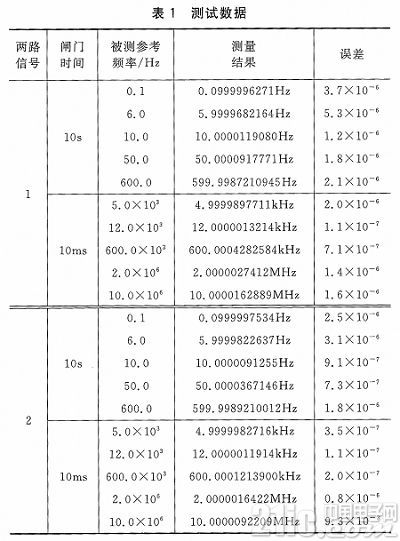

由式(3)可以看出,测量频率的相对误差与被测信号频率的大小无关,仅与闸门时间和基准信号频率有关。闸门时间越长,标准频率越高,测频的相对误差就越小。这里选定标准信号频率为48 MHz,闸门时间分别为10 s和10 ms的情况。通过计算可知:闸门时间为10 s时,理论误差为2.083×10-9;闸门时间为10 ms时,理论误差为2.083×10-8。系统电路安装调试成功后,对上述结果进行验证。两路输入信号分别取自绿杨牌YB1631信号发生器以及信达牌XD11BH多用信号发生器。被测信号参考频率由Keithley 2000数字万用表测得。测量结果如表1所列。

由表1可知,本设计测量结果的相对精度在10-6以上,基本达到设计精度要求,但是与理论误差相比还有一定差距。原因有两方面:一方面在现有的实验室条件下,没有频率精度更高的频率计,故以其为标准计算得到的误差只能作为参考,更高的测量精度无法验证;另一方面是系统本身存在误差。

结语

本系统以PSoC芯片CY8C29666为核心,以多周期同步测频法为基础,充分利用了PSoC芯片内部集成的功能模块资源,完成了两路信号频率测量系统的设计。其硬件电路简单,提高了频率测量的精度,实现了高集成度、高速和高可靠性。同时,由于PSoC器件的体积和功能优势,简化了系统的设计,进一步降低了成本。

- 基于PSoC的防高压电容测量设计与实现(03-27)

- 测量位置的PSoC微控制器与LVDT(07-06)

- 用于位置测量的PSoC微控制器与LVDT(09-29)

- 一种基于PSoC的无线静载仪采集系统的设计(01-27)

- 天平的设计(10-24)

- UART自动验证平台(12-16)