基于FPGA的QCM湿度测量系统程序设计与仿真

锁存器result_latch保存至下一次测量结束。在整个系统中复位信号周期性出现在保持时间末刻,以使计数寄存器下一次从0开始计数。

3.3 频率差值计算模块

获得两个通道的频率值后,根据频差计算公式(2),将两者送入减法器中。

△F=Fo-Fs (2)

减法器采用BCD码减法,按以下规则顺序执行:

1)比较大小,如果被减数大于或等于减数,差为正,符号记为0;如果减数小于被减数,将被减数与减数的位置对调,差为负,符号记为1;

2)按照二进制法逐位减法运算;

3)从最低位开始包括被减数、减数、差的每4位组成一组,高位不够4位用零补齐;

4)如果每一组的被减数大于减数,则若差大于9,则差减去6,其他不变;

5)如果每一组的被减数小于等于减数,则若差大于5(最小1组大于6),则差减去6,其他不变;

6)修正后的结果即为频率差。

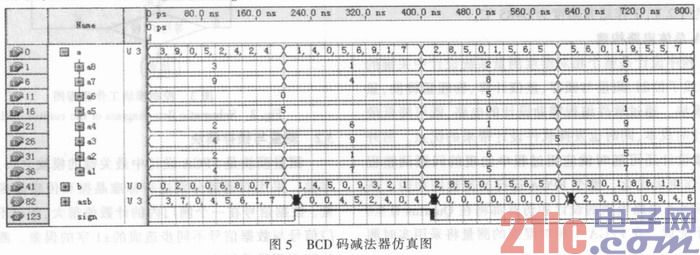

随机设计了几组数据进行仿真测试,如图5所示,经比对,结果正确。其中a8至a1为被减数a的高位至低位,即为标准晶振的频率值;b8至b1为减数b的高位至低位,即为传感晶振的频率值;差为asb8至asb1,符号为sign。

3.4 物理量转换模块

在20%至85%这段相对湿度区间,频率差与相对湿度值之间的曲线接近线性。设计中频率差与相对湿度值之间的转换以查找表的形式来实现,一个湿度范围对应一组频率差。通常情况下,由于材料、制作工艺的不同,频率差的变化也会有所不同。为了仿真,假定相对湿度变化1%时,频率差变化2个值。

3.5 显示驱动模块

后端显示用LCD1602液晶屏构成。由于1602中命令和数据共享总线,首先需要对其初始化,目的就在于对总线状态、显示样式的设置。初始化过程为清屏→显示状态设置→工作方式设置→CG RAM设置→DD RAM设置。一旦初始化结束后,就可以将结果等内容在液晶屏上动态显示。

4 总体电路测试与仿真

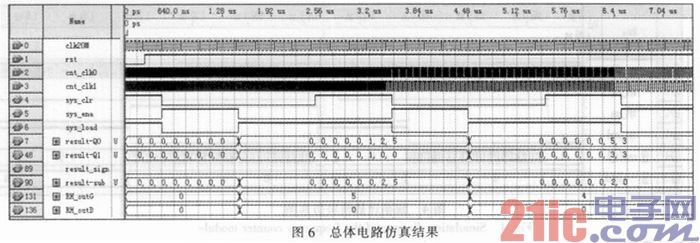

为便于仿真观察,程序上对时钟和信号周期进行了修改,但设计思路不变,不影响整个的工作流程。打开Quartus II的仿真器,插入输入输出信号,依照实际情况给出输入信号波形,仿真结果如图6所示。其中clk20M为20 MHz的时钟信号,经20分频,得到一个周期为的闸门信号(实际中为2s)。因为传感石英晶体质量因受湿度的影响而增加,其谐振频率随之下降,故传感晶振频率总小于标准晶振。cnt_clk0、cnt_ clk1分别为两个通道的频率信号,其周期设置在0 s~3.4μs为8 ns和10 ns,在3.4~6.4 μs至为19 ns和30 ns,在6.4~7.3μs至为35 ns和50 ns;系统一开始清零;result_Q为通道0的频率测量值,result_Q1为通道1的频率测量值。在仿真中取频率的最大变化为50,每1%的相对湿度,有2的变化。由图可看出,当系统在接到清零信号后,立即对计数寄存器进行了数据复位。当测量周期结束后,分别得到以下数值:在0 s~3.4μs这一段,通道0计数值为125,通道1为100,差值为25,湿度为50%;在3.4~6.4μs至,通道0为53,通道1为33,差值为20,湿度为40%。

5 结论

设计运用了功能强大的FPGA作为湿度测量系统的主要部件,充分发挥其高度集成的内部资源和弥补了硬件上设计的漏洞和误差。文中对相对湿度测量系统中的FPGA部分的程序进行了设计说明和仿真,给出总体电路的仿真结果。证明了设计方案的可行性,体现了软件结合设计所带来的简便性和实用性。

如果将该FPGA测量平台与其他外围硬件电路组合,即可完成湿度测量系统的设计,同时也可用于特殊气体的检测。

石英晶体 湿度测量 FPGA EP2C8Q208C8N 电路仿真 相关文章:

- 石英晶体振荡线路的回路分析(10-12)

- 实际电容法石英晶体谐振器负载谐振频率测量技术研究(10-22)

- 石英晶体谐振频率测量系统(08-06)

- DDS技术在高频石英晶体测试系统中的应用(01-17)

- 实际电容法石英晶体谐振器负载谐振频率测量技术研(07-16)

- 石英晶体谐振器静电容测量方法(07-25)