石英晶体振荡线路的回路分析

一个晶体振荡电路必然会存在一定范围的误差,问题是如何了解这个误差范围,并将误差值控制在最小的范围以内。

振荡线路回路分析的目的:

一个晶体振荡电路必然会存在一定范围的误差,问题是如何了解这个误差范围,并将误差值控制在最小的范围以内。

振荡电路主要有三种误差来源:

第一种:石英晶体单元本身就存在有不同的精度(也就是容许误差)。

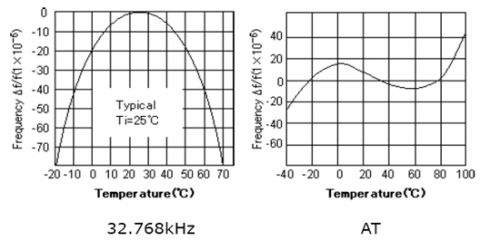

第二种:误差来源是石英晶体的温度特性,也就是频率随温度变化会出现偏差的现象。

图1 石英晶体频率-温度特性曲线。

第三种:误差来源来自振荡电路上的外围元器件配置,这些组件包括石英晶体、半导体IC、外围电阻/电容,以及PCB 走线。

进行振荡电路回路分析的目的,就是为了检视石英晶体在整个振荡电路中是否得到理想的匹配。透过回路分析,研发人员可以在电路设计阶段就了解石英晶体振荡电路的匹配状况,避免在量产后才发生问题,因为再更改设计很不容易。

回路分析要点

振荡电路回路分析包含三个基本的面向,介绍如下:

1. 频率容许误差(Frequency Tolerance)的量测:

频偏误差的计算公式如下:

频偏误差=(量测频率值–中心频率值)/中心频率值x 1,000,000(得出的单位为ppm)。

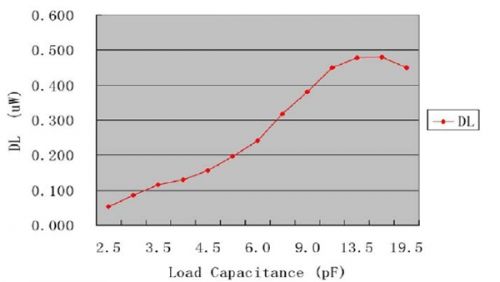

2. 驱动功率(D.L.,Driver Level):

计算公式为:P (uW)= I^2 x Re

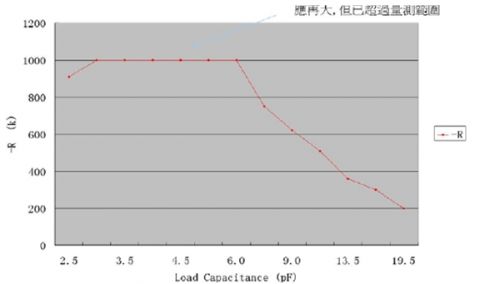

3. 负性阻抗(也称为起振余量):-R

负性阻抗代表振荡线路的起振余量状况,也就是这个电路的健康度,即石英晶体在驱动下容不容易被起振。负性阻抗的判断基本值是石英晶体最大ESR 值的3~5 倍。

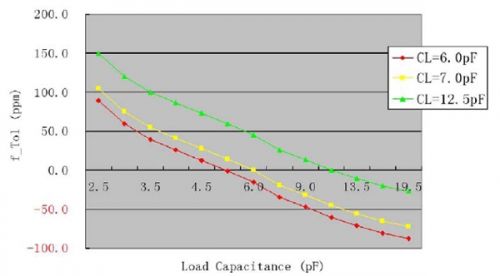

实际操作的时候主要改变负载电容的匹配,那么我们来看一下负载电容和各项参数的关系:

负载电容与频率容许误差的关系图:电容变大,频率变慢;电容变小,频率变快

负载电容与驱动功率的关系图:当负载电容变小时,驱动功率也会变小

负载电容与负性阻抗的关系图:当负载电容变小时,负性阻抗会变大

案例分析:

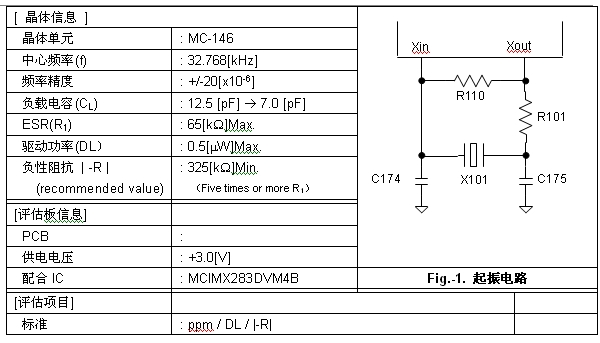

晶体信息

客户在应用MC-146的过程中发现会有10%左右的晶体起振时间过长、甚至不起振的现象发生。需要对电路设计进行测试来找到问题的原因和解决方法。

根据客户提供参数测试得到如下数据:

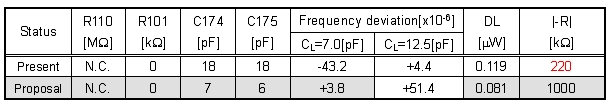

从测试结果看客户初始选择 Cl= 12.5pF 的MC-146 进行设计,匹配电容C174=C175=18Pf, 测得精度为 +4.4 ppm 满足应用要求。同时 DL= 0.119?W 也小于0.5 ?W的要求。

但是我们看到 –R 值为 220 k? 不满足 –R> 5* ESR 的要求。 该设计存在起振缓慢或停振的风险,因此需要对回路的器件参数进行重新设定。

重新设定的原则是:使振荡回路得到的参数指标都满足设计要求。

经过测试发现 Cl=12.5pF 的MC-146 在该系统的所有情况下都不能满足全部的参数要求,因此需要更换晶体单元。

结果显示当使用Cl=7 pF 的MC-146 的时候,匹配电容C174=7pF C175=6 pF, 测得精度为 +3.8 ppm 满足应用要求。同时 DL= 0.081?W 也小于0.5 ?W的要求。-R 值为 1000 k???

远远大于 5倍ESR (325 k?)。因此推荐客户使用该参数匹配的电路设计,可以保证得到稳定可靠的时钟频率。

- DDS函数信号发生器的优点(09-28)

- 时钟的抖动测量与分析(03-16)

- 智能电表内部构造深度拆解:电表如何智能?(07-23)

- 抗振晶体振荡器相位噪声测试方法的对比研究(10-22)

- 基于LabVIEW的晶体振荡器测试系统(10-18)