示波器那些事儿--之存储深度

存储深度表现在物理介质上其实是某种存储器的容量,存储器容量的大小也就是存储深度。示波器采集的样点存入到存储器里面,当存储器保存满了,老的采样点会自动溢出,示波器不断采样得到的新的采样点又会填充进来,就这样周而复始,直到示波器被触发信号“叫停”,每“叫停”一次,示波器就将存储器中保存的这些采样点“搬移”到示波器的屏幕上进行显示,这两次“搬移”之间等待的时间被称为“死区时间”。有个形象的比喻,存储器就像一个“水缸”,“水缸”的容量就是“存储深度“,如果使用一个“水龙头”以恒定的速度对水缸注水,水龙头的水流速就是“采样率”,当水缸已经被注满水后,水龙头仍然在对水缸注水,这时候水缸里的水有一部分就会溢出来,但水缸的总体容量是保持不变的。

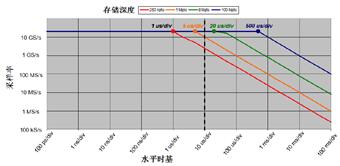

存储深度=采样率 × 采样时间,对于数字示波器,其最大存储深度是一定的,但是在实际测试中所使用的存储长度却是可变的。 在存储深度一定的情况下,存储速度越快,存储时间就越短,他们之间是一个反比关系。同时采样率跟时基(timebase)是一个联动的关系,也就是调节时基档位越小采样率越高。存储速度等效于采样率,存储时间等效于采样时间,采样时间由示波器的显示窗口所代表的时间决定。譬如当时基选择10μs/div,因为水平轴是10格(有些示波器是12格或14格),因此采样时间为100μs,在1Mpts的存储深度下,当前的实际采样率为1M÷100μs =10 GS/s , 如果存储深度只有250Kpts,那当前的实际采样率就只要2.5GS/s了。

某些厂商制造的示波器,当前的最大存储深度可以在菜单中设置。一旦设置好当前的最大存储深度之后,调节水平时基,随着采样时间的增加,示波器的存储深度会自动增加,这个过程中采样率保持不变;存储深度随采样时间增加到当前设置的最大存储深度后,如果继续增加采样时间,采样率会自动下降,存储深度保持不变。但是在有些情况下,因为采样率和采样时间的步进是在固定的若干个档位下跳变,并不是连续细调的,两者相乘不一定和最大存储深度的数值相同,这时候示波器可能会自动调整当前的采样率或存储深度,使得它们三者满足乘积关系。

由存储关系式知道:提高示波器的存储深度可以间接提高示波器的采样率,当要测量较长时间的波形时,由于存储深度是固定的,所以只能降低采样率来达到,但这样势必造成波形质量的下降;如果增大存储深度,则可以以更高的采样率来测量,以获取不失真的波形。

下图中第一个图形表明在采样率足够的前提下,观察多个周期的样本,需要的存储深度很长,图示中需要36个采样点。第二个图形采样率依然保持方便,但存储深度变小,只有9个采样点,因此只能采样一个周期多点的波形。第三个波形仍然是存储深度很小,只有9个采样点,但仍然要采样和第一个图形一样多个周期的波形,其结果是采样率变小,测量得到的波形就会失真。

对于高端示波器,存储器芯片一直是核心技术,示波器中的ADC速率太快,普通的存储介质根本来不及在这么短的时间内“吞吐”那么大的数据量。譬如ADC的采样速率是20GS/s,也就是说每秒要采集20G个点,而每个点是由8个0和1组成,如果ADC的输出是完全按照串行数据传送到存储器中,那么传输速率就是160Gbps,现在的PCI-Express 3.0的速率是8 Gbps,最高速的高速芯片在单板上传输的速率是25 Gbps,但还不成熟,也没用到示波器上,高速的ADC采样点怎么传输到存储器中,这是一个难题。其实,这么高速的ADC也不可能是单芯片设计的,内部是由很多的2.5GS/s或1.25S/s、250MS/s的小的ADC交织拼接的。

随着示波器技术的发展,目前存在两种架构模式,一种是基于PC平台的,另外一种是嵌入式的,主要是基于FPGA实现的。随着DDR内存速率的提高和FPGA计算能力的增强,现在基于FPGA计算平台的存储器芯片已经不再神秘,多是采用工业上的DDR内存颗粒了,因此存储深度这个指标在不顾及存储的采样点是否真实的被显示、被分析的情况下,可以做的特别大了。但往往真实情况是,虽然存储深度很高,但显示的采样点数和分析的采样点数

示波器存储深 相关文章:

- 浅谈示波器的存储深度(01-12)

- 关于示波器的存储深度(01-05)

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)