数字存储示波器基础一

时间:01-06

来源:互联网

点击:

你可能还记得,第一章中我们谈到,普通模拟示波器CRT上的P31荧光物质的余辉时间小于1ms。在有些情况下,使用P7荧光物质的CRT能给出大约300ms的余辉时间。只要有信号照射荧光CRT就将不断显示信号波形。而当信号去掉以后使用P31材料的CET上扫迹迅速变暗,而使用P7材料的CRT上扫迹停留时间稍长一些。

那么,如果信号在一秒钟内只有几次,或者信号的周期为数秒至珍长,甚至于信号只发生一次,那又将会怎么样呢?在这种情况下,使用我们上面介绍过的模拟示波器则几乎乃至于完全不能观察这些信号。

因此我们需要找到在荧光物质上保持信事情轨迹的方法。为达到这一目的而采用的一种老式方法是使用一种称为存储示波管的特殊CRT。这种示波管的荧光物质后面装有栅网,通过在栅网上充载电荷的方法存贮电子束的路径。这种示波管价格很昂贵又比较脆弱,并且只能耐有限的时间内保持轨迹。

数字存储的方法克服了所有这些缺点,并且还带来了很多附加的特色,下面列出部分特点:

·可以显示大量的预触发信息。

·可通通过使用光标和不使用光标的方法进行全自动的测量。

·可以长期贮存波形。

·可以在打印机或绘图仪上制作硬考贝以供编制文件之用。

·可以反新采集的波形和操作人员手工或示波器全自动采集的参考波形进行比较。

·可以按通过/不通过的原则进行判断。

·波形信息可用数学进行处理。

何谓数字存储 从字意上不难看出,所谓数字存储就是在示波器中以数字编码的形式来贮存信号。

当信号进入数字存储示波器,或称DSO以后,在信号到达CRT的偏转电路之前(图18),示波器将按一定的时间间隔对信号电压进行采样。然后用一个模/数变换器(ADC)对这些瞬时值或采样值进行变换从而生成代表每一个采样电压的二进制字。这个过程称为数字化。

图18 数字存储示波器的方框图 获得的二进制数值贮存在存储器中。对输入信号进行采样的速度称为彩样速率。采样速率由采样时钟控制。对于一般使用情况来说,采样速率的范围从每秒20兆次(20MS/s)到200MS/s。

存储器中贮存的数据用来在示波器的屏幕上重建信号波形。

所以,在DSO中的输入信号接头和示波器CRT之间的电路不只是仅有模拟电路。输入信号的波形在CRT上获得显示之前先要存贮到存储器中去我们在示波器屏幕上看到的波形总是由所采集到数据重建的波形,而不是输入连接端上所加信号的立即的、连接的波形显示。

采样和数字化 数字存储分两步来实现。第一步,获取输入电压的采样值。这是通过采样及保持电路来完成的,见图19。

图19 基本的采样保持电路 当开关S闭合时,输入放大器A1,通过开关S对保持电容进行充放电,而当开关S断开时保持电容上的电压就不再变化,缓冲放大器A2将此采样值送往模/数变换器(ADC),ADC则测量此采样电压值,并用数字的“字”的形式表示出来。

模/数字变换器围绕一组比较器而构成,见图20,每一个比较器都检查输入睬样电压是高于或低于其参考电压。如果高于其参考电压则该比较器的输出为有效;反之则输出为无效。

图20 模数变换器基本电路 各个比较器的参考电压彼此略有不同,这此参考电压都是用一个电阻链从一个基准电压源而得到的。对于某一采样电压值来说,若干个比较器输出为有效,而其余的比较器输出为无效,接着ADC中的编码变换器就把该采样电压值变为一个“数字”,并将其送往数字存储器。

这种类型的ADC称为闪其速式(flash)模/数字变换器。因为它能在“一闪”间把一个模拟输入电压变换为一个“数字”。除此之外,还可以使用其它类型的模/数变换器,。其模/数变换是由几步动作来完成的,但是其缺点是完成一个采样压的变换所需时间较长。

模/数变换器和垂直分辨率 ADC通过把采样电压和许多参考电压进行比较来确定采样电压的幅度。构成ADC所用的比较器越多,其电阻链越长,ADC可以识别的电压层次也赵多。这个特性称为垂直分辨率,垂直分辨率越高,则示波器上的波形中可以看到的信号细节越小(见图21)。图21 垂直分辨对显示波形的影响 垂直分辨率用比特来表示,垂直分辨率就是构成输出的字的总比特数(即数字输出字的长度大小)。

这样ADC可以识别并进行编码的电压层次数可以用下式来计算:

层次数=2比特数 多数示波器使用比特的模/数变换器,所以能够按28=256个不同的电压层次来表示信号电平,这样就能够提供足够的细节以便研究信号和进行测量,在这种垂直分辨率下,可以显示的最小分辩率号步进值大约和CRT屏幕上光点的直径大小相同,代表采样电压值的一个ADC输出字包含8个比特,并称为一个字节。

在现实当中,增加垂直分辨率的限制因素之一是成本问题,在制造ADC时,输出字每多增加一个比特,就需要将所用的比较器数增加一倍并使用更大的编码变换器,这样一来就使得ADC电路在电路板上占据大一倍的芯片空间,并消耗多一倍的功率(这又将进一步影响周围电路)结果,增加垂直分辨率又带了价格的提高。 时基和水平的分辨率 在数字存储示波器中,水平系统的作用是确保对输入信号采集足够数量的采样值,并且每个采样值取自正确的时刻,和模拟示波器一样,水平偏转的速度取决于时基的设置(s/格)。

构成一个波形的组全部的采样叫作一个记录,用一个记录可以重建一个或多个屏莫的波形,一个示波器可以贮存的采样点数称为记录长度或采集长度,记录长度用字节或千字节来表示,1千字节(1KB)等于1024个采样点。

通常,示波器沿着水平轴显示512采样点,为了便于使用,这些采样点以每格50个采样点的水平分辨率来进行显示,这就是说水平轴的长为512/50=10.24格。

据此,两个采样之间的时间间隔可按下式计算:

采样间隔=时基设置(s/格)/采样点数

若时基设置为1ms/格,且生格有50个采样,则可以计算出采样间隔为:采样间隔=1ms/50=20us

采样速率是采样间隔的倒数:采样速率=1/采样间隔

通常示波器可以显示的采样点数是固定的,时基设置的改变是通过改变采样速率来实现的,因此一台特定的示波器所给出的采样速率只有在某一特定的时时设置之下才是有效的。在较低的时基设置之下,示波器使用的采样速率也比较低。

设有一台示波器,其最大采样速率为100MS/s那么示波器实际使用这一采样的速率的时基设置值应为

时基设置值=50样点×采样间隔

=50/采样速率

=50/(100×106)

=500ns/格

了解这一时基设置值是非常重要的,因为这个值是示波器采集非重复性信号时的最快的时基设置,使用这个时基设置时示波器能给出其可能的最好的时间分辨率。

此时基设置值称为“最大单次扫描时基设置值”,在这个设置值之下示波器使用“最大实进采样速率”进行工作。这个采样速率也就是在示波器的技术指标中所给出的采样速率。

实用上升时间 在很多示波器应用场合,都要进行信叼开关我的测量,即测量上升时间和下降时间。

从第一章我们已经知道,示波器的上升时间决定了该示波器能够精密进行测量的最快瞬变我对于模拟示波器来说,上升时间特性。对于模拟示波器来说,上升时间特性完全取决于示波器的模拟电路。

如果DSO,则示波器可以采集到的最快的瞬变特性不仅取决于其模拟电路,也取决于其时间分辨率。为了正确的进行上升时间的测量,必须在我们关心的信号边缘上采集到足够的细节信息,这就是说,在瞬变期间必须采集很多采样点。这个上升时间称为DSO的有用上升时间。并且其时间值是时基设置值的函数。

我们将在本书的练习部分(第六章)更详细的讨论上升时间测量的问题。

最大捕捉频率及香农(Shannon)采样准则 当人们最初探索将信号进行数字化的时候研究工作就已揭示,为了很好的恢复原来的信号,在进行信号数字化的时候就要求采样时钟的频率至少应为信号本身所包含的最高频率的两倍,这个要求通常称为香农采样定理。

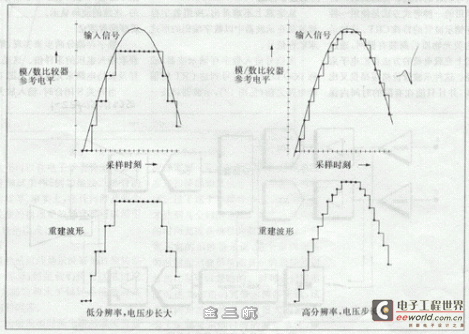

然而,这项研究工作是针对通信应用领域而并非针对示波器为进行的,现在来看图22。从图中看出。当使用两倍于信号频率的采样时钟时。信号频率确实可以恢复。使用恰当的波形重建装置我们就可可得到和原始的波形十分相象的波形。但是问题睦的是这样简单吗?

现在我们设想在进行波形的数字化时仍然使用相同的采样时钟,但是将采样点选在和原来略为不同的时刻,不定在信号的峰值点,这样一来,信号的幅度信息就会严重失误,甚至可能完全丢失,事实上。如果采样点准确地取在信号地过零零碎碎点(见图22下图)那么由于所有的采样取到的采值均为零零碎碎,我们将完全观测不到信号。

那么,如果信号在一秒钟内只有几次,或者信号的周期为数秒至珍长,甚至于信号只发生一次,那又将会怎么样呢?在这种情况下,使用我们上面介绍过的模拟示波器则几乎乃至于完全不能观察这些信号。

因此我们需要找到在荧光物质上保持信事情轨迹的方法。为达到这一目的而采用的一种老式方法是使用一种称为存储示波管的特殊CRT。这种示波管的荧光物质后面装有栅网,通过在栅网上充载电荷的方法存贮电子束的路径。这种示波管价格很昂贵又比较脆弱,并且只能耐有限的时间内保持轨迹。

数字存储的方法克服了所有这些缺点,并且还带来了很多附加的特色,下面列出部分特点:

·可以显示大量的预触发信息。

·可通通过使用光标和不使用光标的方法进行全自动的测量。

·可以长期贮存波形。

·可以在打印机或绘图仪上制作硬考贝以供编制文件之用。

·可以反新采集的波形和操作人员手工或示波器全自动采集的参考波形进行比较。

·可以按通过/不通过的原则进行判断。

·波形信息可用数学进行处理。

何谓数字存储 从字意上不难看出,所谓数字存储就是在示波器中以数字编码的形式来贮存信号。

当信号进入数字存储示波器,或称DSO以后,在信号到达CRT的偏转电路之前(图18),示波器将按一定的时间间隔对信号电压进行采样。然后用一个模/数变换器(ADC)对这些瞬时值或采样值进行变换从而生成代表每一个采样电压的二进制字。这个过程称为数字化。

存储器中贮存的数据用来在示波器的屏幕上重建信号波形。

所以,在DSO中的输入信号接头和示波器CRT之间的电路不只是仅有模拟电路。输入信号的波形在CRT上获得显示之前先要存贮到存储器中去我们在示波器屏幕上看到的波形总是由所采集到数据重建的波形,而不是输入连接端上所加信号的立即的、连接的波形显示。

采样和数字化 数字存储分两步来实现。第一步,获取输入电压的采样值。这是通过采样及保持电路来完成的,见图19。

模/数字变换器围绕一组比较器而构成,见图20,每一个比较器都检查输入睬样电压是高于或低于其参考电压。如果高于其参考电压则该比较器的输出为有效;反之则输出为无效。

这种类型的ADC称为闪其速式(flash)模/数字变换器。因为它能在“一闪”间把一个模拟输入电压变换为一个“数字”。除此之外,还可以使用其它类型的模/数变换器,。其模/数变换是由几步动作来完成的,但是其缺点是完成一个采样压的变换所需时间较长。

模/数变换器和垂直分辨率 ADC通过把采样电压和许多参考电压进行比较来确定采样电压的幅度。构成ADC所用的比较器越多,其电阻链越长,ADC可以识别的电压层次也赵多。这个特性称为垂直分辨率,垂直分辨率越高,则示波器上的波形中可以看到的信号细节越小(见图21)。

这样ADC可以识别并进行编码的电压层次数可以用下式来计算:

层次数=2比特数 多数示波器使用比特的模/数变换器,所以能够按28=256个不同的电压层次来表示信号电平,这样就能够提供足够的细节以便研究信号和进行测量,在这种垂直分辨率下,可以显示的最小分辩率号步进值大约和CRT屏幕上光点的直径大小相同,代表采样电压值的一个ADC输出字包含8个比特,并称为一个字节。

在现实当中,增加垂直分辨率的限制因素之一是成本问题,在制造ADC时,输出字每多增加一个比特,就需要将所用的比较器数增加一倍并使用更大的编码变换器,这样一来就使得ADC电路在电路板上占据大一倍的芯片空间,并消耗多一倍的功率(这又将进一步影响周围电路)结果,增加垂直分辨率又带了价格的提高。 时基和水平的分辨率 在数字存储示波器中,水平系统的作用是确保对输入信号采集足够数量的采样值,并且每个采样值取自正确的时刻,和模拟示波器一样,水平偏转的速度取决于时基的设置(s/格)。

构成一个波形的组全部的采样叫作一个记录,用一个记录可以重建一个或多个屏莫的波形,一个示波器可以贮存的采样点数称为记录长度或采集长度,记录长度用字节或千字节来表示,1千字节(1KB)等于1024个采样点。

通常,示波器沿着水平轴显示512采样点,为了便于使用,这些采样点以每格50个采样点的水平分辨率来进行显示,这就是说水平轴的长为512/50=10.24格。

据此,两个采样之间的时间间隔可按下式计算:

采样间隔=时基设置(s/格)/采样点数

若时基设置为1ms/格,且生格有50个采样,则可以计算出采样间隔为:采样间隔=1ms/50=20us

采样速率是采样间隔的倒数:采样速率=1/采样间隔

通常示波器可以显示的采样点数是固定的,时基设置的改变是通过改变采样速率来实现的,因此一台特定的示波器所给出的采样速率只有在某一特定的时时设置之下才是有效的。在较低的时基设置之下,示波器使用的采样速率也比较低。

设有一台示波器,其最大采样速率为100MS/s那么示波器实际使用这一采样的速率的时基设置值应为

时基设置值=50样点×采样间隔

=50/采样速率

=50/(100×106)

=500ns/格

了解这一时基设置值是非常重要的,因为这个值是示波器采集非重复性信号时的最快的时基设置,使用这个时基设置时示波器能给出其可能的最好的时间分辨率。

此时基设置值称为“最大单次扫描时基设置值”,在这个设置值之下示波器使用“最大实进采样速率”进行工作。这个采样速率也就是在示波器的技术指标中所给出的采样速率。

实用上升时间 在很多示波器应用场合,都要进行信叼开关我的测量,即测量上升时间和下降时间。

从第一章我们已经知道,示波器的上升时间决定了该示波器能够精密进行测量的最快瞬变我对于模拟示波器来说,上升时间特性。对于模拟示波器来说,上升时间特性完全取决于示波器的模拟电路。

如果DSO,则示波器可以采集到的最快的瞬变特性不仅取决于其模拟电路,也取决于其时间分辨率。为了正确的进行上升时间的测量,必须在我们关心的信号边缘上采集到足够的细节信息,这就是说,在瞬变期间必须采集很多采样点。这个上升时间称为DSO的有用上升时间。并且其时间值是时基设置值的函数。

我们将在本书的练习部分(第六章)更详细的讨论上升时间测量的问题。

最大捕捉频率及香农(Shannon)采样准则 当人们最初探索将信号进行数字化的时候研究工作就已揭示,为了很好的恢复原来的信号,在进行信号数字化的时候就要求采样时钟的频率至少应为信号本身所包含的最高频率的两倍,这个要求通常称为香农采样定理。

然而,这项研究工作是针对通信应用领域而并非针对示波器为进行的,现在来看图22。从图中看出。当使用两倍于信号频率的采样时钟时。信号频率确实可以恢复。使用恰当的波形重建装置我们就可可得到和原始的波形十分相象的波形。但是问题睦的是这样简单吗?

现在我们设想在进行波形的数字化时仍然使用相同的采样时钟,但是将采样点选在和原来略为不同的时刻,不定在信号的峰值点,这样一来,信号的幅度信息就会严重失误,甚至可能完全丢失,事实上。如果采样点准确地取在信号地过零零碎碎点(见图22下图)那么由于所有的采样取到的采值均为零零碎碎,我们将完全观测不到信号。

数字存储示波 相关文章:

- 基于FIFO IDT7202-12的数字存储示波器(01-07)

- 利用数字存储示波器测量特殊信号(11-02)

- 基于DSP的数字存储示波器的设计方案(03-23)

- 简易数字存储示波器中控制器模块的设计(01-12)

- 基于TFT 彩屏液晶的便携数字存储示波器(01-12)

- 一种数字存储示波器智能触发技术研究(01-12)