生物电阻抗测量系统中弱信号检测技术研究--弱信号检测调理单元设计与实现

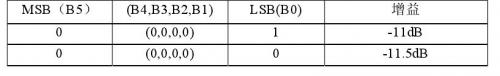

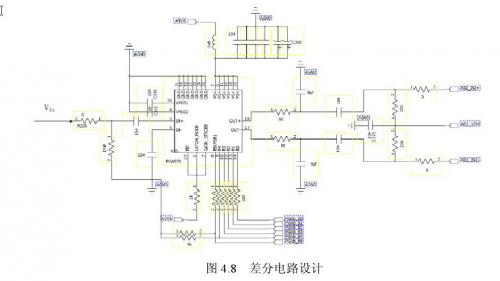

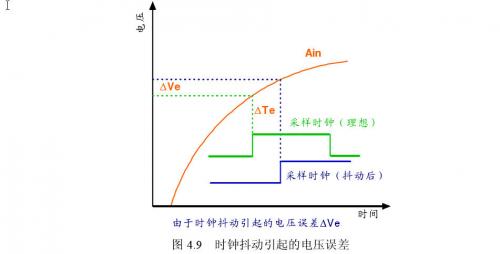

大电路。 PGA870是一款高速全差分可编程增益放大器。它的高带宽、低失真、低噪音特性使它非常适合与14位ADC配合使用,其增益调节范围为-11.5 dB到20dB,增益步幅为0.5dB,增益准确度为0.03dB.频带范围为650MHZ.其内部结构图如图4.5所示。 从图中可以看出,输入差分信号依次经过衰减器、放大器、输出控制器,衰减倍数和放大倍数由控制逻辑位B0-B5和gain strobe、latch mode管脚控制。在power-down状态,静态电流降至2mA,但是增益控制电路仍能保持可编程。 为实现信号增益可控,设计中选择PGA870芯片,因为PGA870有三种配置模式,分别是电平锁存模式,沿寄存模式,组合逻辑方式,由配置管脚gain strobe和latch mode控制,其配置方式如表4.3所示。 图中,为了减小信号反射的幅度,在B0-B5上均串联上一个电阻。为了减小前端直流偏置对本模块的影响,同时考虑到芯片内部已经提供了一个内部参考电压,信号输入端采用交流耦合方式,耦合电容选用较大值0.1uf,以让低频信号无衰减通过。因为放大器的输出电阻只有3.5欧姆,为实现信号的50欧姆端接,输出串联50欧姆电阻。 可编程增益放大的实现由FPGA来完成,如图4.7所示,FPGA通过逻辑控制来确定配置模式,通过控制放大器的B0至B5管脚控制运放的增益。 4.2.4.1 ADC前端电路 生物电阻抗测量系统中,信号采集的是直流信号,对于这种信号,不能用阻容耦合或变压器耦合的方式,宜采用直接耦合放大电路但存在零点漂移。所谓零点漂移是指当输人信号为零时,在放大器的输出端出现一个变化不定的输出信号的现象,简称零漂。前级的漂移被后级放大,因此严重干扰正常信号,级数越多,漂移越严重,甚至使放大器不能正常工作。在电路结构上,采用差分电路是目前应用最广泛的能有效抑制零漂的方法。 1.由两个完全对称的共射电路组合而成。 为了说明差分放大电路抑制共模信号的能力,常用共模抑制比作为一项技术指标来衡量,其定义为放大器对差模信号的电压放大倍数Aud与对共模信号的电压放大倍数Auc之比,称为共模抑制比,英文全称是Common Mode Rejection Ratio,因此一般用简写CMRR来表示。 图中芯片仍为PGA870可变增益放大器,其输出方式为全差分的,能有效的抑制环境中的共模干扰,其CMRR可达到76db,PGA870的输出端采用RC网络进行信号的端接,能有效的减小信号的反射,并采用交流耦合的方式将信号传送至后端ADC芯片。图中信号线ADC_VCM提供差分信号合适的直流偏置,在信号线ADC_IN2+和ADC_IN2-上串接5欧姆的电阻来减小反射过冲电流的大小。 4.3时钟模块设计 4.3.1时钟电路设计分析 时钟对于高速ADC系统而言尤其关键,这是因为时钟信号的时序准确性可以直接影响ADC的动态特性。理想的时钟源是不会抖动的,因此ADC可以精确的在每个固定的时间间隔进行采集,但是实际电路中各种不确定的因素都会造成时钟的抖动。如图4.9所示,这种时序的不确定性带来的结果是采样波形出现一个为eΔV的误差电压,这相当于在原信号上引入了新的噪声,从而ADC的信噪比会受到数据转换过程的影响。

4.2.3.1 PGA870的应用

4.2.3.2可编程增益放大电路的设计

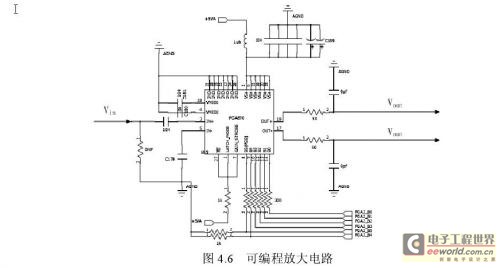

组合逻辑方式的信号延迟最小,实时行相应最好,且配置方式需要的线也最小,只需将B0-B5连接到FPGA管脚上,Gain strobe和Latch mode接到3.3V上就可以了,综上,PGA870的配置方式采用组合逻辑方式,其在电路中的设计图如图4.6所示。

4.2.3.3可编程增益实现方式

PGA870的增益控制实现方式如表4.4所示,表中未列出全部控制组合,其增益按B0至B5变化组合以0.5dB步进。

4.2.4 ADC前端共模抑制模块

差分放大电路又叫差分电路,它能有效的减小由于电源波动和晶体管引起的零点漂移,因而获得广泛的应用。

差分电路的输入端有两个信号的输入,这两个信号的差值,为电路有效输入信号,电路的输出是对这两个输入信号之差的放大。设想这样一种情景,如果存在干扰信号,会对两个输入信号产生相同的干扰,通过二者之差,干扰信号的有效输入为零,这就达到了抗共模干扰的目的。

差分放大电路的特点:

2.电路采用正负双电源供电。

3.极强的共模抑制能力。

4.2.4.2共模抑制比

差模信号电压放大倍数Aud越大,共模信号电压放大倍数Auc越小,则CMRR越大。此时差分放大电路抑制共模信号的能力越强,放大器的性能越好。当差分放大电路完全对称时,共模信号电压放大倍数Auc=0,则共模抑制比CCMR→∞,这是理想情况,实际上电路完全对称是不存在的,共模抑制比也不可能趋于无穷大。

本文采用电路完全对称的差分电路以做到阻抗匹配和ADC前端调理,如图4.8所示:

生物电阻抗测量系统弱信号检 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)