详解差分信号

我们中的大部分都能直观地理解信号是如何沿导线或走线传播的,即便我们也许对这种连接方式的名称并不熟悉——单端模式。术语“单端”模式将这种方式同至少其它两种信号传播模式区分开来:差模和共模。后面两种常常看起来更加复杂。

差模

差模信号沿一对走线传播。其中一根走线传送我们通常所理解的信号,另一根传送一个严格大小相等且极性相反(至少理论上如此)的信号。差分与单端模式并不像它们乍看上去那样有很大的不同。记住,所有信号都有回路。一般地,单端信号从一个零电位,或地,电路返回。差分信号的每一分支都将从地电路返回,除非因为每个信号都大小相

等且极性相反以至于返回电流完全抵消了(它们中没有任何一部分出现在零电位或地电路上)。

尽管我不打算在专栏中就这个问题花太多时间,共模是指同时在一个(差分)信号的线对或者在单端走线和地上出现的信号。对我们来说这并不容易直观地去理解,因为我们很难想象怎样才能产生这样的信号。相反通常我们不会产生共模信号。通常这些都是由电路的寄生环境或者从邻近的外部源耦合进电路产生的。共模信号总是很“糟糕”,许多设计规则就是用来防止它们的发生。

差分走线

尽管看起来这样的顺序不是很好,我要在叙述使用差分走线的优点之前首先来讲述差分信号的布线规则。这样当我讨论(下面)这些优点时,就可以解释这些相关的规则是如何来支持这些优点的。

大部分时候(也有例外)差分信号也是高速信号。这样,高速设计规则通常也是适用的,尤其是关于设计走线使之看起来像是传输线的情况 。这意味着我们必须仔细地进行设计和布线,如此,走线的特征阻抗在沿线才能保持不变。

在差分对布线时,我们期望每根走线都与其配对走线完全一致。也就是说,在最大的可实现范围内,差分对中每根走线应该具有一致的阻抗与一致的长度。差分走线通常以线对的方式进行布线,线对的间距沿线处处保持不变。通常地,我们尽可能将差分对靠近布线。

差分信号的优点

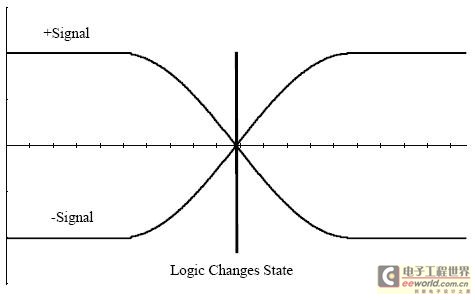

“单端”信号通常参考到某些“参考”电位。这有可能是正的或者是地电压,一个器件的门限电压,或者另外某处的信号。另一方面,差分信号仅参考到与其配对信号。也就是说,如果一根走线(正信号)上的电压比另外一根走线(负信号)高,我们就得到了一个逻辑状态,如果是低,我们就得到另外一个逻辑状态(见图1)。这样有几个好处:

图 1当差分信号曲线交叉时逻辑状态在该点发生改变

时序可以更精确地定义,因为控制一对信号的交点比控制一个关于其他参考电压的绝对电压容易。这也是走线要精确等长的原因之一。任何在源端所进行的时序控制都可以让步,如果信号在不同的时间到达另一端。进一步来讲,如果线对的远端信号没有精确相等且极性相反,共模信号就可能产生并将导致信号时序与EMI问题。

因为除了自身,差分信号没有参考任何其它信号,并且信号交叉的同步可以更有力地控制,差分电路通常可以运行在比类似的单端电路更高的频率上。

因为差分电路对两根走线(两者的信号大小相等极性相反)上信号的差作出响应,得到的净信号两倍于(可比的环境噪声)任一单端信号。因此在其它条件等同的情况下,差分信号有着更大的信噪比及性能。

差分电路对线对信号之间的电位差敏感。但是(相对地)对线上与其它参考电压相比(特别是地)的绝对电位不敏感。因此,相对而言,差分电路对诸如地弹、其它存在于电源和/或地平面的噪声信号以及可能出现在每一根走线中相等的共模信号这样的问题不敏感。

差分信号对EMI和串扰略微免疫。如果线对走得很近,这样任何外部耦合噪声将相等地耦合进线对。这样一来耦合噪声就变成“共模”噪声,而电路对此是(理论上)免疫的。如果导线是“缠绕”(比如双绞线)的,那么对噪声的免疫性就更好。因为我们不能方便地将印制板上的差分走线缠绕起来,把它们尽可能地靠近走线就是最好的办法了。

紧挨着布线的差分对彼此紧密耦合。这种互耦减少了EMI辐射,特别是与单端走线相比。你可以把这个认为是每根走线的辐射彼此大小相等且极性相反,这样彼此的输出就相互抵消了,就像在双绞线中一样!差分走线彼此越靠近,耦合越强,EMI辐射的可能性就越小。

缺陷

差分电路的主要缺陷是走线的增加。因此,如果你的应用中这些优点没有一个是特别重要的,那么就不值得为差分信号以及附带的布线考虑增加面积。但是如果这些优点在你的电路中产生了显著的性能差异,那么增加的布线面积就是我们付出的代价。

重要结论

差分线彼此耦合。这种耦合影响了走线的对外阻抗,因此端接方法 (

差分信号差 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)