详解差分信号

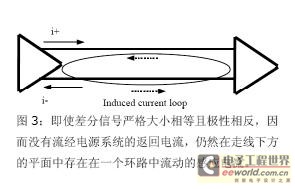

个规则是:走线必须等长。有人激烈地反对这条规则。通常他们的争论的基础包括了信号时序。他们详尽地指出许多差分电路可以容忍差分信号两个部分相当的时序偏差而仍然能够可靠地进行翻转。根据使用的不同的逻辑门系列,可以容忍500 mil 的走线长度偏差。并且这些人们能够将这些情况用器件规范和信号时序图非常详尽地描绘出来。问题是,他们没有抓住要点!差分走线必须等长的原因与信号时序几乎没有任何关系。与之相关的仅仅是假定差分信号是大小相等且极性相反的以及如果这个假设不成立将会发生什么。将会发生的是:不受控的地电流开始流动,最好情况是良性的,最坏情况将导致严重的共模EMI问题。 因此,如果你依赖这样的假定,即:差分信号是大小相等且极性相反,并且因此没有通过地的电流,那么这个假定的一个必要推论就是差分信号对的长度必须相等。差分信号与环路面积:如果我们的差分电路处理的信号有着较慢的上升时间,高速设计规则不是问题。但是,假设我们正在处理的信号有着有较快的上升时间,什么样的额外的问题开始在差分线上发生呢?考虑一个设计,一对差分线从驱动器到接收器,跨越一个平面。同时假设走线长度完全相等,信号严格大小相等且极性相反。因此,没有通过地的返回电流。但是,尽管如此,平面层上存在一个感应电流! 任何高速信号都能够(并且一定会)在相邻电路(或者平面)产生一个耦合信号。这种机制与串扰的机制完全相同。这是由电磁耦合,互感耦合与互容耦合的综合效果,引起的。因此,如同单端信号的返回电流倾向于在直接位于走线下方的平面上传播,差分线也会在其下方的平面上产生一个感应电流。 但这不是返回电流。所有的返回电流已经抵消了。因此,这纯粹 是平面上的耦合噪声。问题是,如果电流必须在一个环路中流动,剩下来的电流到哪里去了呢?记住,我们有两根走线,其信号大小相等极性相反。其中一根走线在平面一个方向上耦合了一个信号,另一根在平面另一个方向上耦合了一个信号。平面上这两个耦合电流大小相等(假设其它方面设计得很好)。因此电流完全在差分走线下方的一个环路中流动(图3)。它们看上去就像是涡流。耦合电流在其中流动的环路由(a)差分线自身和(b)走线在每个端点之间的间隔来定义。 设计规则2 现在EMI 与环路面积已是广为人知了3。因此如果我们想控制EMI,就需要将环路面积最小化。并且做到这一点的方法引出了我们的第二条设计规则:将差分线彼此靠近布线。有人反对这条规则,事实上这条规则在上升时间较慢并且EMI 不是问题时并不是必须的。但是在高速环境中,差分线彼此靠得越近布线,走线下方所感应的电流的环路就越小,EMI 也可以得到更好的控制。 值得一提的是一些工程师要求设计人员去掉差分线下方的平面。原因之一是减小或消除走线下方的感应电流环路。另外一个原因是防止平面上已有的噪声耦合到(推测如此)走线上的低压信号4。 还有一个将差分线彼此靠近布线的理由。差分接收器设计为对输入信号的差敏感而对输入的共模偏移不敏感。也就是说即使(+)输入相对(-)输入仅有轻微的偏移,接收器也会检测到。但是如果(+)和(-)输入一起偏移(在同样的方向),相对而言接收器对这种偏移不敏感。因此如果任何外部噪声(比如EMI 或串扰)等同地耦合到差分线中,接收器将对此种(共模耦合)噪声不敏感。差分线布得越彼此靠近,任何偶合噪声在每根走线上就越相近。因此电路的噪声抑制就越好。 规则2推论 再次假定高速环境中,如果差分线彼此紧挨着布线(为了使其下方的环路面积最小化)那么走线将彼此耦合。如果走线足够长以至于端接成为一个问题,这种耦合就会影响到确切的端接阻抗5的计算。原因是:考虑一个差分线对,线1 和线2。假使它们分别携带信号V1 和V2。因为它们是差分线,V2=V1*V1 在线1 引起一个电流I1 而V2在线2 引起一个电流I2。电流必然是从欧姆定律导出,I=V/Z0,这里Z0 是走线的特征阻抗。现在线1(举例)携带的电流事实上由i1 和k*i2 组成,这里k 是线1 与线2 间的耦合比例。这表明这种耦合的最终效果是线1 上的一个明显的阻抗,这个阻抗等于Z=Z0-Z12这里Z12 由线1 与线2 间的互耦6引起。如果线1 和线2 分得很开,它们之间的耦合就很小,确切的端接阻抗就只是Z0,单端走线的特征阻抗。但是如果走线靠的更近,它们之间的耦合就会增加,这样走线的阻抗与这种耦合成比例地减校这就是说确切的走线端接(为了防止反射)为Z0-Z12,或者某个小于Z0 的值。这对差分对的两根走线都适用。

差分信号差 相关文章:

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)

- 泰克全新VM6000视频测试仪助力数字电视等产品测试 (10-06)