利用AD7616的V型采样实现准同步数据采集

例,用TSPAN = 14μs来计算“V型采样+数据平均”所带来误差的最大值:

对于50Hz (基波),误差最大值为:1 - cos(π * 50Hz * 14μs) < 0.01‰;

对于250Hz (5次谐波),误差最大值为:1 - cos(π * 250Hz * 14μs) < 0.1‰;

对于2550 kHz (51次谐波),误差最大值为:1 - cos(π * 2550Hz * 14μs) < 6.3‰;

从以上的计算结果来看,“V型采样+数据平均”的模式完全可以满足电力系统中保护和测控的精度要求。下一步将会用实验的方法进行验证。

4 AD7616准同步采样的实现

在传统的“MUX模拟开关+单通道ADC”模式中,ADC每收到一个CONVST启动转换控制信号后,仅完成一个通道的转换。这就意味着,要通过“V型采样+数据平均”的方式来实现“准同步采样”,需要处理器 (Processor) 发出一系列的CONVST启动转换控制信号来实现多个通道的采样序列,还要求处理器在每次启动转换之前读出ADC的转换数据,这既增加了处理器的负担,又降低了系统的可靠性。

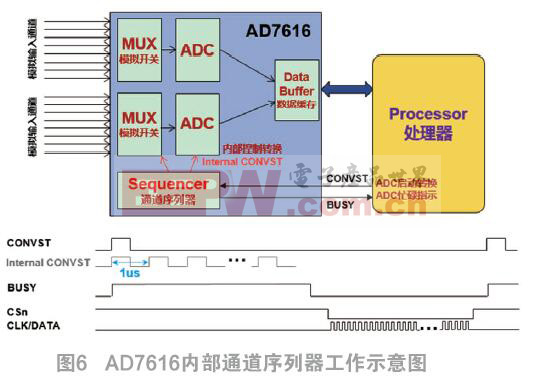

AD7616内部集成了MUX模拟开关和SAR型ADC,特别之处在于还集成有突发模式 (Burst Mode) 和灵活的通道序列器 (Flexible Sequencer) 。当AD7616工作在软件模式 (Software Mode) 下,通过设置序列栈寄存器 (Sequencer stack registers) ,处理器只需要发出一个CONVST启动转换控制信号,AD7616将会自行完成所有设置通道的转换,并把每一次的转换结果放在数据缓存区中,待全部通道转换完成后,AD7616将BUSY忙碌指示信号置低,等待处理器读取所有通道的转换结果。AD7616与处理器的连接及内部通道序列器的示意图如图6所示。

AD7616内部有两个高速ADC核,称为A核和B核。通道的序列栈寄存器地址为0x20到0x3F,总共包含32个寄存器,由用户编程来实现1到32个预定的采样序列。每个寄存器的宽度为16bit,其中 [7:4] bit定义为BSEL,用来设定B核的转换通道, [3:0] bit定义为ASEL,用来设定A核的转换通道。寄存器中的 [8] bit定义为SSREN,是通道转换序列的结束控制位,如果设定为0,AD7616将调入下一个序列寄存器的设置进行转换,如果设定为1,通道转换序列在完成本次转换后结束。转换通道的选择,除了模拟输入通道VIN0 ~ VIN7,还可以选择内部Vcc,内部LDO,或者固定输出一个标志字0x5555或0xAAAA。AD7616序列栈寄存器的描述如图7所示。

在应用中,处理器上电后,需要对AD7616内部的通道序列栈寄存器进行初始化。初始化完成后,需要把AD7616寻址寄存器的REGADDR[4:0]设置为00000,使得AD7616的状态为输出ADC转换数值。假定按照图3的模式进行设置,即采样通道顺序为“VIN0→VIN1→VIN2→…→VIN6→VIN7→VIN6→… →VIN2→VIN1→VIN0”。处理器与AD7616并口连接的情况下,序列栈寄存器的配置代码参考图8所示。在这样的配置下,VIN0 ~ VIN6通道都分别被采样了两次,数据平均由处理器来计算,这样准同步采样时刻正好对应于VIN7通道采样点在时间轴的位置。

应用中特别需要注意的是:软件模式下,完成AD7616所有寄存器的配置后,由于需要一个CONVST启动转换来使得所有寄存器配置都有效,因此AD7616第一次转换的输出结果是不可靠的,应用中需要把第一次的转换数据丢弃,数据手册中也把这第一次的转换称为“伪转换” (Dummy Convert)。另外,为了实现一次CONVST完成序列栈寄存器中全部通道的转换,在AD7616配置寄存器 (0x02 – Configuration Register) 中的SEQEN、BURSTEN位 (bit5, bit6) 都必须使能。AD7616的工作流程图参考图9所示。

5 测试验证

配合理论分析,同时搭建了AD7616的测试系统,如图10所示。验证系统中,信号源为Audio Precision 2712,输出高SNR (信噪比) 、低THD (总谐波失真) 的正弦波供AD7616进行测试。处理器采用Cortex-M4内核的混合信号控制处理器 ADSP-CM408F,AD7616采集的数据通过串口 (UART) 发送给PC电脑,使用Visual AnalogTM软件分析AD7616数据获得交流性能指标 (SNR和THD) ,使用Microsoft Excel? 运行DFT算法获得幅值和相位信息。

测试中,AD7616的采样序列按照图4的“V型采样+数据平均”模式进行设置,但为了让实验的结果对比更为容易,同时排除AD7616各通道间性能差异的影响,序列栈寄存器设置为对同一个输入通道VIN0进行连续多次采样,这样在一次“V型采样”中,VIN0先后总共被采样15次,分别定义为S0~S14,如图11所示。

数据计算中,把S0与S14配对并取均值,S1与S13配对取均值,以此类推,但S7不参与任何平均计算。这样,将(S0+S14)/2,(S1+S13)/2,(S2+S12)/2,(S3+S11)/2,(S4+S10)/2,(S5+S9)/2,(S6+S8)/2 的平均值结

AD7616 V型采样 准同步采样 201710 相关文章:

- 线缆测试仪的通用适配器设计(09-27)

- 频宽、取样速率及奈奎斯特定理(09-14)

- 为什么要进行信号调理?(09-30)

- IEEE802.16-2004 WiMAX物理层操作和测量(09-16)

- 为任意波形发生器增加价值(10-27)

- 基于PCI 总线的高速数据采集系统(09-30)