具有多个电压轨的FPGA和DSP电源设计实例(一)

大多数FPGA和DSP内核和I/O轨的直流容差依然是±5%;然而,一些内核轨及其它一些芯片电源轨的容差已经降低到±3%。对某个特定的芯片,容差范围的低端(–5或–3%)通常是确保某些性能要求(如DSP运行速度)可达的最小电压。该范围的较高端可能接近于该芯片的绝对最高运行电压。理解电源的直流容差的计算方法不仅对保证系统的性能很重要,对保证系统的可靠性也很重要。直流容差不包含由负载阶跃的暂态所产生的电压骤降(dip)。负载阶跃的暂态发生在由POL转换器供电的数字器件快速提高负载电流要求的时候。直接影响电源直流容差的因素包括参考电压容差、反馈电阻容差以及该芯片的线调解指标和负载调解指标。

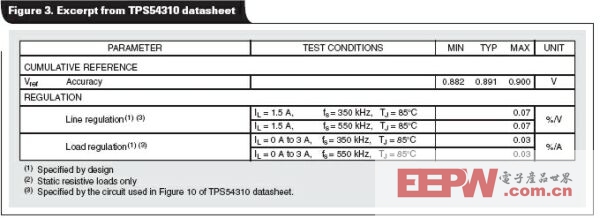

图3给出的例子摘自TPS54310可调降压开关转换器的性能说明书。

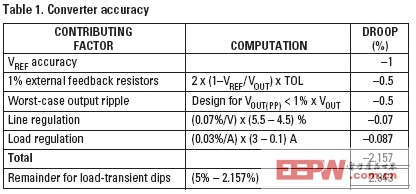

假设输入轨为5V ±10%,直流输出负载的范围为100mA到3A,表1计算了1.2V ±5%的输出电压在负载暂态过程中可以骤降(仍在调解范围内)的百分比。线调解指标和负载调节指标随器件变化,甚至来自同一家电源IC制造商的器件也是如此,所以在计算中使用它们时必须小心。大多数最新的转换器都带有电压前馈,几乎消除了输出电压对输入电压的依赖并使线调解几乎可忽略。负载调节是电源芯片的环路增益的函数;较高的环路增益有较好的负载调解能力。请注意,许多输出电压固定并带有内部补偿的转换器的输出电压精度更高,因为输出电压可以通过调整内部反馈电阻进行设定。

在表1的例子中,在输出电压下降到–5%最低容差之前,只有1.2V的2.843%或34.1mv的空间可用于负载瞬时骤降。在转换器做出响应之前,电源轨上的电容必须能够提供这个负载电流,否则该电压将降到规范以下。为处理负载暂态过程,可以把不同容量且串联电阻低的电容和电感并联。如何确定这个“解耦网络”的电容容量以及它们将如何影响转换器的响应时间,本文将在后面进行讨论。

|

|

- IR2110驱动电路的优化设计(03-15)

- 基于CAN通信的电源监控系统的设计(04-06)

- 浅谈LDO的压差(Dropout)和功耗(Power Dissipation)(02-07)

- TPS54350在信号处理系统中的应用(06-09)

- AD7656的原理及在继电保护产品中的应用(06-18)

- 基于Motorola M12 GPS接收机实现继电保护同步检测(06-11)