基于LT1641的双路热插拔电路设计

0 引言

很多大型数据系统中都会采用"背板+插件板"结构。这样,在更换维护插件板时,通常都希望在不影响系统工作的情况下带电插拔。电路上电或带电插拔时,一般会产生很大的启动电流和电压波动,这些现象将影响设备的正常工作,甚至导致整个系统的损害。当一块插件板插入工作背板或者从工作背板拔出时,插件板上附加电容的充放电会给工作背板提供一个低阻抗,此时背板到插件板的高涌入电流可能会烧毁连接器和电路元件,或者暂时使背板陷落以导致系统重启。这种现象就是热插拔现象。

所谓热插拔(Hot Swap),就是允许用户在不关闭系统或不切断电源的情况下,取出和更换损坏的硬盘、电源或板卡等部件,换句话说,就是系统出现故障的部件能进行带电更换。从而提高系统对灾难的及时恢复能力、扩展性和灵活性。热插拔过程一般分为三个步骤:一是物理连接过程,分插入和拔出两种情况;二是硬件连接过程,主要指的是与系统相连的硬件层的电气连接;三是软件连接过程,主要指的是与系统相连的软件层的连接。

本文主要针对某大型数据系统带有双路电压结构的插件板进行热插拔电路的设计。所讨论的热插拔概念主要是针对硬件的热插拔,即在带电状态下安全地插拔电路板。其基本要求是不影响系统的运行,以便于系统的维护和重新配置。其典型应用有基站、磁盘冗余阵列(RAID)、远程接人服务器、网络路由器、网络交换器以及ISDN系统等。

1 电路设计

某大型数据系统插件板由一路48 V工作电压和一路3.3 V待机电压供电。该插件板耗电高达1000 W(48 V/20 A),插件热插拔时两路电压均需支持热插拔。两路电压的上电要求有先后顺序,48 V必须在3.3 V产生之后才能输出。插件板推入带电背板时,3.3 V热插拔电路首先上电。在3.3 V稳定输出后,48 V热插拔电路开始工作。如果3.3 V热插拔电路工作不正常,则48 V热插拔电路将被强行关闭。

1.1 3.3 V缓冲电路设计

由于3.3 V电源是一个待机电源,属于低电压(3.3 V)、小电流(<2 A)。所以在缓冲电路设计过程中,主要考虑的是控制浪涌电流,同时力求电路设计简单实用。因此,3.3 V热插拔电路由电容C1、稳压管D1和MOSFET U1构成。通过对连接在U1栅、源极之间的电容C1充电可达到限制浪涌电流的目的。为了避免插件板插入带电背板时产生很大的浪涌电流。要求插件板板上的电压应当斜坡式上升,其电压上升过程的持续时间大约为30ms。

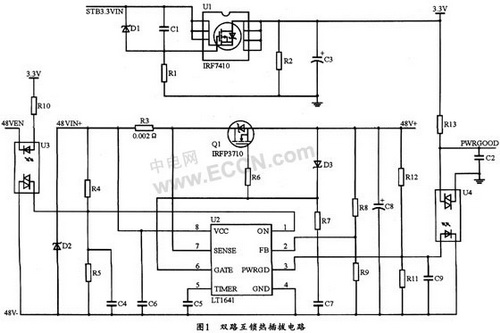

本电路中的MOS管选用P沟道的IRF7410,该器件的最大工作电流ID为-16 A,开启电压VGS(th) 最大值为0.9 V,其电路如图1所示。

当插件板插入背板时,热插拔电路中的RC电路开始工作,t<0时,热插拔电路已处于稳态,电容电压uc(0_)为0;t=0时,开关闭合,电源VIN开始对电容进行充电。此后在初始时刻,由于uc(0+)=uc(0_)=0,电容相当于短路,其充电电流i(0+)=[VIN-uc(0+)]/R=VIN/R。之后,随着时间t的延长,电容电压uc(t)逐渐增大,充电电流随之减小。当t→∞时,uc(∞)=VIN,充电电流i(∞)=0,此时电容如同开路,充电停止,电路进入稳态。根据KVL及元件的伏安关系,可得出换路后电路的方程为:

1.2 48 V热插拔电路设计

48 V热插拔电路因为其电压高、电流较大,所以,要求具具有更高的可靠性和可维护性,此时,上述普通的热插拔电路已经不能满足该电路的设计需要。而现在流行的各种热插拔控制器可在极小的封装内提供多种功能(如具有可编程设置的电流检测门限、反馈限流、短路保护、过压保护、欠压锁定等),正好满足该电路设计的需要。因此,48 V热插拔电路可在热插拔控制器的基础上搭建其外围电路。

由于该路的电源电压48 V,工作电流为20A。结合对各种芯片的比较,本设计最终选定的热插拔控制器是正压热插拔控制器LT1641。LT1641是一款完全集成的8引脚Hot Swap热插拨正压控制器,它允许将电路板安全的从带电的背板中插入或拔出,而不会在背板的电源上产生脉冲干扰。它可通过控制外部的N沟道MOSFET,来使电路板的电压按设定的速率线性增加,直至达到电源电压。同时,该器件还具有可编程的折返式限流特性,可通过电子断路器提供短路故障保护及限流功能。其工作电压范围为9~80 V。

LT1641的引脚ON可用来检测欠压锁定阀值,并且在发生故障后复位器件;FB脚为电源就绪比较器输入,从输出端到FB再到GND应接一个电阻分压器,以监控输出电压,此外,FB还可用作折返限流功能反馈;PWRGD为开漏电源就绪输出,当VFB高于VFBH时,PWRGD为高,当VFB低于VFBL时,PWRGD为低;TIMER为定时输入,在TIMER到GND间

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)