高速PCB中旁路电容的分析

,它将灌入一定量的电流到电源或者地系统中。为了减小电源或者地噪声,就需要采取措施来减小灌入到电源或者地平面当中的电流量。为了切实做到这一点,理论上需要将电源或者地管脚串联一个阻抗,这个阻抗必须足够大,最好比芯片电源地管脚的输出阻抗还大。但串联这样一个大的阻抗是不现实的,因为如果这样的话,将会在芯片内部产生更大的地弹噪声或者电源扰动,导致芯片不能够正常工作。因此正确的做法还应该是设法将噪声通过低阻抗的回路引到地平面上去。通常的做法是给芯片的电源管脚加旁路电容。下面简单的分析了电容的四种放置方式。

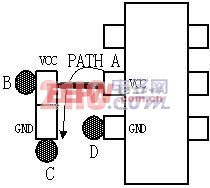

如图7及图8(a)所示,为旁路电容的一种放置方式。将芯片的地管脚直接通过一个低阻抗的过孔D(一般过孔的寄生电感约为1~2nH)连接到地平面上,这样芯片地管脚上的地弹噪声将通过过孔流入到地平面上,抑制了地弹噪声对芯片的影响。芯片的电源管脚通过一小段传输线(通常约为50~80mil长,寄生电感约为1~1.6nH)连接到电容的电源盘垫上,电容的电源盘垫和地盘垫直接通过过孔连接到电源平面和地平面上,这样电源管脚到地平面之间也将有一条低阻抗的通路,有效的克服了电源管脚上的电源噪声对芯片的影响。同时旁路电容附近的电源层上的噪声也将通过过孔B、旁路电容、过孔C这样一条低阻抗通道流入到地平面上,这样的放置方式有效的抑制了噪声对芯片以及电源和其他系统的影响。

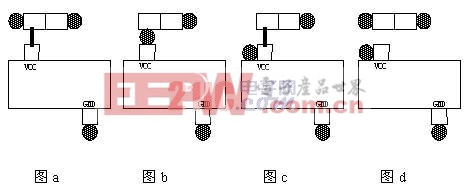

如图8(b)所示,将过孔B放在电容电源管脚和芯片电源管脚之间,这样将增加通路A的环路电感,当电容和芯片不是位于同一层时,一般采用这种方式。

如图8(c)所示,将电容电源管脚处的电源过孔B改打到接近芯片电源管脚A处,这种放置方式类似于上述第二种放置方式,将导致环路电感的增加,此方式应避免。

如图8(d)所示去掉电容电源管脚和芯片电源管脚之间的传输线,而将芯片电源管脚直接通过一个过孔连接到地平面上,电容电源管脚和芯片电源管脚之间通过大的电源平面连接到一起,这样通路A包括:两个过孔、一个电源平面、一个电容,也同样增加了环路的电感,而且噪声将对电源平面带来不可预知的影响,另外还增加了过孔的数量,减少了板子上的布线面积。此方式也应尽量避免。

6 结束语

当前数字系统板级频率越来越高,各种EMI问题也越来越严重。合理的选择和使用旁路电容是消除EMI、获得电源完整性的一个关键方面。而且,随着半导体技术的进一步发展,电容也在不同的更新换代以满足高速电路设计的要求。因此,旁路电容选择、旁路电容的摆放等问题需要不断的进行深入探讨。

- 具扩展频谱频率调制的低EMI DC/DC稳压器电路(12-24)

- EMI/EMC设计讲座(三)传导式EMI的测量技术(07-20)

- 扩展射频频谱分析仪可用范围的高阻抗FET探头(07-14)

- 开关电源基于补偿原理的无源共模干扰抑制技术(08-27)

- 开关电源的无源共模干扰抑制技术(11-12)

- 省电设计使DDS更适合便携应用(12-19)