中频解调电路中的I2C总线接口电路

在该中频解调的接口电路中,基于I2C总线传输协议,通过对状态机与控制逻辑的优化设置,只需要1个3位的状态机便可实现电路的使能、启动、终止、应答、复位、选址等功能,电路得到了最优化,且通过地址选择位的增加,防止了芯片地址冲突,极大地改善了电路的可靠性及稳定性。

1 I2C总线的特点及数据传输

1.1 总线特点

I2C总线是由数据线SDA和时钟线SCL构成的双向串行总线,I2C总线上的所有节点,如主控器、外围器件、接口模块都连接到SDA,SCL上,在总线备用时,SDA和SCL都保持高电平,I2C不工作时SCL嵌位在低电平。为了使总线上所有电路的输出都能实现“线与”功能,I2C总线接口电路的输出端必须是漏极开路结构,输出端要接上拉电阻。

1.2 总线的数据传输格式

I2C总线数据传送格式按图1进行。首先由主控设备发出起始信号(S),即SDA在SCL高电平期间由高电平跳变为低电平,然后主控器发送1个字节的数据。首先传送的是最高位(MSB)。在传输了每个字节之后,必须要有接收设备发出1位应答信号。

起始信号后的第1个字节是寻址字节,寻址字节的高7位是接收设备的地址,第8位是方向位,“O”发送数据(写状态),“1”接收数据(读状态)。寻址字节后面可以有很多数据字节,每个字节后都要有一位发自接收设备的应答信号。在结束与该接收设备通信时,主控设备

必须发出终止信号(P),即在时钟线SCL为高电平期间,SDA由低电平跳变为高电平。

2 中频解调电路I2C总线接口的实现

电视中频解调电路中的I2C总线接口主要由输入滤波器、地址寄存器、移位寄存器、控制寄存器、状态机与控制逻辑、读状态寄存器、输出模式寄存器等构成,如图2所示。其中,输入滤波器具有I2C总线逻辑兼容电平,输入时钟与内部时钟同步,可滤除部分干扰信号。控制逻辑作为控制核心控制着每一部分的状态。地址寄存器存放着自己的7位地址,用来与接收到的地址比较。移位寄存器、输出模式寄存器与读状态寄存器端口并行相接,各存储着8位数据字节。

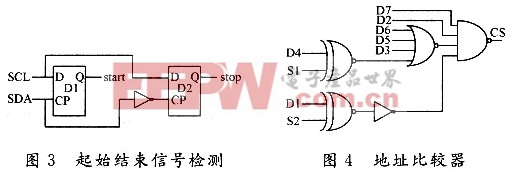

(1)起始信号与结束信号检测。起始信号与结束信号的检测由2个下降沿D触发器和1个反相器构成,如图3所示。D1在SDA从高电平跳变到低电平时触发,此时只有当SCL保持高电平时,Start才为1,即检测到起始信号。同理,D2在SDA从低电平跳变到高电平时触发,此时只有当SCL保持高电平时,Stop才为1,即检测到结束信号。

(2)地址检测。根据设计要求,I2C总线每次通信输入8位地址数据和控制数据,电路进行地址比较以后,如果地址正确,则接收控制数据。为了防止地址冲突,增加了地址选择位,具体实现如图4所示。D7~D1为发送的数据地址,由于S1,S2是可设置端口,有4种组合,即总线接口有4个地址,分别为1000010,100001l,1001010,100101l,只有当D7~D1为100S101S2时,选址成功,即可以有效解决地址冲突。

(3)数据串并与并串的转换。电路中,串行数据转换为并行数据、并行数据转换为串行数据主要由移位寄存器完成。它以并行方式与输出模式寄存器和读状态寄存器相连;以串行方式与数据线SDA相连。发送的数据由读状态寄存器装载到数据寄存器中。发送后数据又从串行通道返回数据寄存器中,接收数据时,数据寄存器装入SDA线上的数据。

(4)内部总线状态的检测。读状态寄存器连接着内部总线的8位状态位S0~S7,在读状态时,该寄存器将内部总线的状态读进去,再以并行方式传给移位寄存器,移位寄存器以串行的方式传给数据线,即内部总线状态被主控器读取,如图5所示。

(5)并行端口的扩展。根据芯片功能的需要,设置了4组输出模式寄存器,分别为调整模式寄存器、备用寄存器、开关模式寄存器、数据模式寄存器。寄存器个数可根据芯片功能的需要进行并行扩展,由于每一组寄存器都对应着相应的子地址,所以每一组寄存器对应相应的时钟CPl,CP2,CP3,CP4和控制端C1,C2,C3,C4。这些时钟和控制端由1个带控制端的2/4译码器输出,所以每次只有1组寄存器工作,如图5

所示。

(6)状态机与控制逻辑的设置与优化。状态机与控制逻辑作为I2C接口的控制中心,主要用于控制I2C接口电路的使能、启动、终止。图5给出寄存器组图的应答、复位、选址及中断请求等。通过对状态机与控制逻辑的优化设置,仅使用3位状态作为状态机的状态端,在满足更多功能的基础上,电路更易于实现。如图6所示,3个触发器的输出Q18,Q15,Q16为状态机的状态,Qd0~Qd8为移位寄存器的输出,HL91为移位寄存器的可控复位端,G111为地址检测位,HL22为应答位,C5,C6为移位寄存器与读状态寄存器的控制端。

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 电源设计小贴士 2:驾驭噪声电源(01-01)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)