Blackfin处理器低功耗设计

摘要:Blackfin处理器广泛应用于便携音视频产品等嵌入式系统,低功耗设计直接影响产品使用时间。文中从时钟频率、工作模式、片内外设、内核电压等方面,说明了Blackfin处理器低功耗设计的具体方法,根据实际应用实现对系统功耗的灵活控制与调节,最大程度上延长系统的有效使用时间。

关键词:DSP;Blackfin;低功耗

Blackfin处理器功耗由内部功耗、外部功耗和实时钟功耗组成。内部功耗由内部动态电流和静态电流引起。外部功耗取决于处理器内外设的使用情况,在不同的应用场合,片内外设的使用有所不同,外部功耗也会不同。实时钟功耗一般处于特定范围之内,工作温度为25~85℃时,实时钟功耗范围为0.067~0.1825mW。Blackfin系列处理器提供了动态电源管理功能,灵活的对时钟频率、工作模式及内核电压进

行调整,以Blackfin533为例阐述Blackfin系列处理器低功耗设计的具体方法。

1 时钟频率控制

现代DSP芯片中大量使用CMOS FET(Complementary Metal-oxide Semiconductor FET互补金属氧化物场效应管)开关,稳定时或者处于完全打开状态(很低的负载),或者处于完全关闭状态,但是在两种状态转换过程中会产生漏电流,所以开关频率很高时,FET充放电会引起很大的电源功耗。因此,通过降低系统时钟频率可以有效降低系统功耗。

Blackfin533通过外部时钟输入引脚CLKIN接收外部时钟源(10~40 MHz)的时钟输入,再通过锁相环(PLL),电路模块产生内核时钟(CCLK)和系统时钟(SCLK),通过设置PLL相关寄存器实现对CCLK和SCLK的频率控制。PLL系统如图l所示。

CCLK和SCLK均由VCO(Voltage-ControlledOscillator-压控振荡器)输出的时钟分频后得到。VCO输出时钟频率由PLL控制寄存器(PLL_CTL)设置,CCLK和SCLK对VCO的分频因子由PLL分频寄存器(PLL_div)设置。PLL_CTL各位说明如表1所示。

对于不同的DF和MSEL值,VCO输出相应的时钟频率,对应关系如表2所示。

需要注意的是VCO最小输出时钟频率为50 MHz,最大输出频率为内核时钟CCLK频率的最大值。对BlackfinBF533,CCLK最大值为600 MHz,而BF532/531的CCLK最大值为400 MHz。所以VCO输出频率不应超出范围50MHz~CCLK。

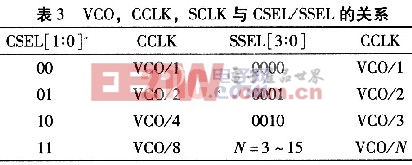

通过设置PLL分频寄存器PLL_div中的CSEL(PLL_div的4~5位)确定CCLK,设置SSEL(PLL_div的0~3位)确定SCLK,具体对应关系如表3所示。

由于SCLK频率不能高于CCLK的频率,所以在对SSEL参数设置时,需要确定当前CCLK的频率。

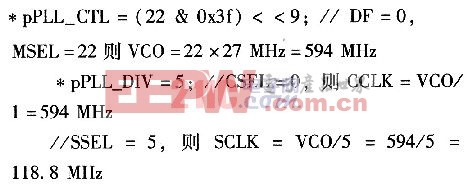

假设外部时钟输入CLKIN=27 MHz,将CCLK设置为594 MHz(27×22),SCLK设置为118.8 MHz(594/5),程序代码如下

2 工作模式转换

Blackfin533具有4种工作模式:全速、激活、睡眠、深度睡眠,功耗大小关系为:全速>激活>睡眠>深度睡眠。不同模式下处理器的内核电压及时钟设置不同,如表4所示。所以灵活调整系统的工作模式可以有效的降低系统的功耗。

在转换工作模式时,应该明确处理器当前的工作模式,而系统的工作模式由PLL控制寄存器(PLL_CTL)中的PLL_OFF,BYPASS,STOPCK和PDWN状态位共同确定。图2说明了各种工作模式转换之间的联系以及转换条件。

通过设置PLL_CTL寄存器实现工作模式的转换,新的设置不会立即生效,需要先执行下面的一个程序段

从当前工作模式转换至另一个工作模式的具体过程简述如下

(1)设置唤醒请求,目的:将处理器唤醒,使PLL_CTL中新的设置生效以便进入新的工作模式。

(2)按模式转换条件,设置PLL_CTL。

(3)禁止一切中断,将处理器置入空闲状态,等待唤醒请求。

(4)唤醒后恢复中断,PLL_CTL中设置的新值开始生效,处理器进入新的工作模式,继续执行其他指令。

默认状态下,所有的中断都能产生1个唤醒请求,即当1个中断产生时,处理器内核就会收到1个唤醒请求,如果此时处于空闲状态,则会退出此状态,处理相应(中断)程序。通过系统中断唤醒使能寄存器(SIC_IWR)设置中断与唤醒请求之间的对应关系,其中24~31位保留,其他位分别对应了不同的中断源,如定时器中断、看门狗定时器中断、DMA中断等,某一位如果置1,则相应中断发生时就会产生1个唤醒事件。系统复位后,SIC_IWR中的所有位均为1。

工作模式转换的关键就是对PLL_CTL的设置,这就要求确认系统当前的工作模式,再根据图2所示的转换条件设置PLL_CTL寄存器。另外必须设置唤醒请求,因为它有助于确定处理器何时被唤醒,进入预期的工作状态。

下面是一个从全速模式到激活模式转换的实例:

对唤醒请求进行设置,本例中利用看门狗定时器中断来产生这个唤醒请求。

(1)设置定时器的计数值:通过看门狗计数寄存器(WDOG_CNT)设置。

(2)设置相应事件:当定时器计数至O时产生中断,即看门狗控制寄存器(WDOG_CTL)第3位置1,其余位为0。

(3)利用看门狗中断产生唤醒请求:SIC_IWR寄存器第24位置1,其他位为0,使能看门狗中断唤醒请求。

- IR2110驱动电路的优化设计(03-15)

- 基于CAN通信的电源监控系统的设计(04-06)

- 浅谈LDO的压差(Dropout)和功耗(Power Dissipation)(02-07)

- TPS54350在信号处理系统中的应用(06-09)

- AD7656的原理及在继电保护产品中的应用(06-18)

- 基于Motorola M12 GPS接收机实现继电保护同步检测(06-11)