基于VHDL 的矩阵键盘及显示电路设计

摘 要:为了有效防止机械式键盘按键抖动带来的数据错误,这里在Quartus Ⅱ开发环境下,采用VHDL 语言设计了一种能够将机械式4 ×4 矩阵键盘的按键值依次显示到8 个7 段数码管上的矩阵键盘及显示电路。仿真结果表明,所设计的矩阵键盘及显示电路成功地实现了按键防抖和按键数据的准确显示。以ACEX1K系列EP1K30QC208 芯片为硬件环境,验证了各项设计功能的正确性。

FPGA/ CPLD 在数字系统设计中的广泛应用,影响到了生产生活的各个方面。在FPGA/ CPLD 的设计开发中,V HDL 语言作为一种主流的硬件描述语言,具有设计效率高, 可靠性好, 易读易懂等诸多优点 。作为一种功能强大的FPGA/ CPLD 数字系统开发环境,Altera 公司推出的Quart us Ⅱ,为设计者提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、快速处理和器件编程,为使用V HDL 语言进行FPGA/ CPLD 设计提供了极大的便利 。矩阵键盘作为一种常用的数据输入设备,在各种电子设备上有着广泛的应用,通过7 段数码管将按键数值进行显示也是一种常用的数据显示方式。在设计机械式矩阵键盘控制电路时,按键防抖和按键数据的译码显示是两个重要方面。本文在Quart us Ⅱ开发环境下,采用V HDL语言设计了一种按键防抖并能连续记录并显示8 次按键数值的矩阵键盘及显示电路。

1 矩阵键盘及显示电路设计思路

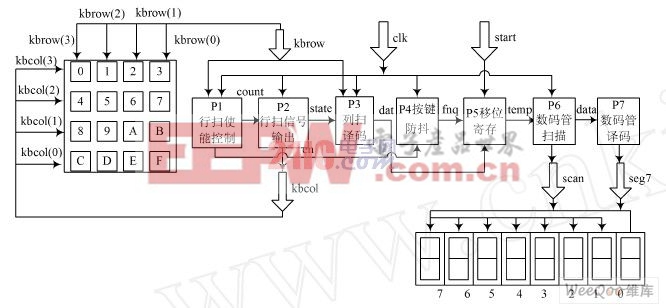

矩阵键盘及显示电路能够将机械式4 ×4矩阵键盘的按键值依次显示到8 个7段数码管上,每次新的按键值显示在最右端的第0 号数码管上,原有第0~6号数码管显示的数值整体左移到第1~7号数码管上显示,见图1 。总体而言,矩阵键盘及显示电路的设计可分为4 个部分:

(1) 矩阵键盘的行及列的扫描控制和译码。该设计所使用的键盘是通过将列扫描信号作为输入信号,控制行扫描信号输出,然后根据行及列的扫描结果进行译码。

(2) 机械式按键的防抖设计。由于机械式按键在按下和弹起的过程中均有5~10 ms 的信号抖动时间,在信号抖动时间内无法有效判断按键值,因此按键的防抖设计是非常关键的,也是该设计的一个重点。

(3) 按键数值的移位寄存。由于该设计需要在8 个数码管上依次显示前后共8 次按键的数值,因此对已有数据的存储和调用也是该设计的重点所在。

(4) 数码管的扫描和译码显示。由于该设计使用了8 个数码管,因此需要对每个数码管进行扫描控制,并根据按键值对每个数码管进行7 段数码管的译码显示。

2 矩阵键盘及显示电路的实现

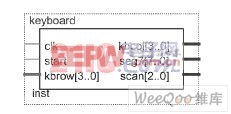

本文所设计的矩阵键盘及显示电图2 所示。其中, clk 为时钟信号输入端(频率可为1 024~32 768 Hz) ; start 为清零控制端;kbrow 为列扫描信号输入端; kbcol 为行扫描信号输出端; scan 为数码管地址扫描信号输出端; seg7 为数码管显示信号输出端。

图1 矩阵键盘及显示电路原理图

图2 矩阵键盘及显示电路的电路符号

限于篇幅,在此不详述所设计矩阵键盘及显示电路的全部V HDL 代码,只对部分重要代码段落进行详细说明。

如图1 所示,全部代码由7 个进程(process) 组成。其中,进程P1 和P2 用于对列扫描输入信号kbrow 进行读取,并通过或非运算产生行扫描使能控制信号en 对行扫描输出信号kbcol 进行控制,并生成一个与kbcol 对应的状态信号state。若没有按键被按下( 即kbrow =“0000”) ,则en =‘1’,行扫描输出信号kbcol 不断循环扫描各行;若有按键被按下,en =‘0’,则行扫描停止,并锁存当前kbcol 的值。进程P1 和P2 的代码如下:

进程P3 使用“case ?when”语句,根据状态信号state 的值(即kbcol 的值) 和列扫描输入信号kbrow 的值进行按键值译码, 生成一个4 位二进制按键数值信号dat ,用以记录当前按键值。例如,当kbcol =“0010”,kbrow =“0001 ”时“B”键按下, dat =“1011”。进程P3 的代码在此不再赘述。进程P4 和P5 用于按键的防抖和按键值的移位寄存。通过将行扫描使能控制信号en 不断赋给一个8 位二进制变量reg8 ,再将reg8 赋给8 位二进制信号key ,实现对按键状态的记录,然后通过对key的各位数值进行与运算,生成防抖控制信号f nq。一旦有按键按下,en =‘0’,则即便是按键在抖动,key 中至少也有1 位数值为‘0’,从而使f nq =‘0’。只有当按键再次弹起,并且在连续8 个时钟周期内不再有新的按键按下,key 的数值全为‘1’,则f nq =‘1’,f nq产生一个上升沿,从而触发按键数值信号dat 进入数值寄存信号temp (32 位二进制数) 的第0 ~ 3 位, 并将temp 原来的第0~27 位左移到第4~

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 适合高效能模拟应用的线性电压稳压器(07-19)

- TPS54350在信号处理系统中的应用(06-09)

- 基于FPGA的三相PWM发生器(06-23)

- 嵌入式 POL DC/DC 转换器设计(07-22)

- 电源管理与转换的整合可简化电源系统设计(07-24)