一种高速连续时间Sigma-Delta ADC设计

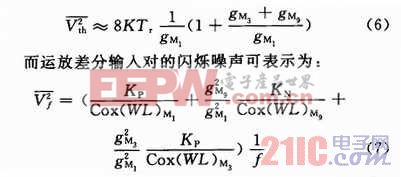

由式(6)和(7)可以看出,在设计中为了降低噪声,可以将晶体管M1的跨导设计得较大,将晶体管M3和M9的跨导设计得尽量小一些。同时,为了减小运算放大器的输入失调,要尽量增大输入管M1和M2的面积,减小其有效的栅源电压面积。最终设计中输入差分对M1和M2的宽长比为W/L=6/0.2。

仿真显示,在各工艺角下,运算放大器最差的性能是在sf下仍可达到DC Gain=66 dB,GBW=960 MHz。

2.2 四输入一位可再生比较器

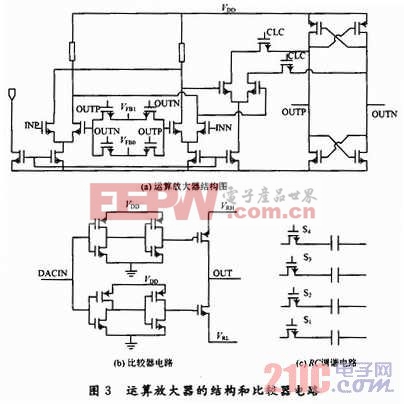

系统中采用的比较器结构如图3(a)所示,该比较器在结构上分为3个部分。第一部分为一个四输入的前置运算放大器,用来比较电压和提高比较器的比较速度。中间一级首先将比较的电压转换为电流,在利用两个由时钟控制的开关的电阻将电流信号转换为电压差送到latch对处进行比较,此级的目的是防止 KickBack噪声对输入信号的影响。最后一级为2个latch对,利用其正反馈特性迅速比较出所需要的结果。电压VFB1和VFB0用来实现系统建模中的系数b3,通过输出端OUTP和OUTN来实现反馈电压极性的控制。通过仿真得出,比较器的延时小于1 ns。

2.3 D/A转换器

本文采用的D/A转化器的结构如图3(b)所示。两个参考电压VRH和VRL分别为1.4 V和O.4 V(即差分参考电压为1 V)。电路具有反相功能,由输入电压的高低来确定反馈电压为VRH或VRL。考虑输出端的寄生电容,仿真显示,该电路延时小于1 ns。

2.4 RC调谐结构

该系统中采用RC积分滤波结构,系统的滤波系数是由电阻与电容乘积的绝对值决定。但在现今CMOS工艺中,电阻与电容的绝对值变换范围可达±25%。所以必须采用RC调谐电路来保证所需的RC乘积的值。系统仿真显示,RC乘积值变化范围在±6%以内可以使系统的SNR仅下降1 dB。采用的RC调谐电路如图3(c)所示。4个电容的阻值分别为C1=150 fF,C2=300 fF,C3=600 fF,C4=1.2 pF。通过对开关信号S1,S2,S3和S4电平高低的控制,可以使电容实现最大2.25 pF,最小150 fF的值。

3 芯片实现

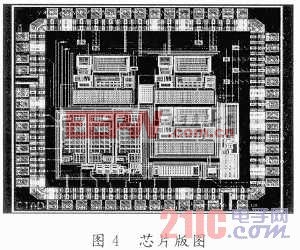

在TSMC O.18 μm工艺下绘制的系统版图如图4所示。芯片所需的时钟信号由外部的低抖动信号发生器提供,时钟信号尽量靠近反馈到输入级的DAC以减小延时。版图中模拟电路部分与高速数字部分分隔以减小影响。

4 实验结果

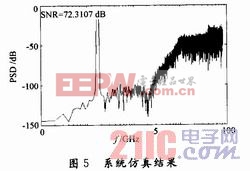

通过Candence提取系统版图后仿真电路,在不同工艺角下对使用HSpice对系统进行后仿真,得到系统SNDR如图5所示(TT工艺角下),最大SNDR可达63.6176 dB,输入差分信号幅度为O.55 V。

针对CT Sigma-Delta ADC各种结构对时钟抖动的忍受能力这一问题,将本文结构与其他论文进行对比,结果如表1所示。可见,该设计对时钟抖动的忍受能力是很强的。

5 结语

采用TSMC O.18μm CMOS工艺,在1.8 V电源电压下设计了一款连续时间Sigma-Delta ADC调制器,完成了电路设计和版图绘制。经后仿真验证此Sig-ma-Delta ADC调制器带宽达到5 MHz,信噪比SNDR可达63.6 dB。芯片在硅片上所占面积为1.5 mm×1.5 mm,而其调制器本身所占面积只有O.9 mm×0.9 mm,功耗仅为32 mW。与同类设计进行比较,该设计对时钟抖动的忍受能力是很强的。

ADC 相关文章:

- S3C2440A嵌入式手持终端电源管理系统设计(01-11)

- 基于CAN通信的电源监控系统的设计(04-06)

- 基于MSP430单片机的电源监控管理系统(04-20)

- 适用于全球交流电源的单节锂离子电池充电器设计(06-07)

- GPIB芯片TNT4882在多路程控电源中的应用(06-08)

- AD7656的原理及在继电保护产品中的应用(06-18)