一种高速连续时间Sigma-Delta ADC设计

摘要:在TSMC O.18 μm CMOS工艺下设计了一款宽带宽、低功耗的连续时间Sigma-Delta ADC调制器。该调制器可以应用于无线通信、视频、医疗和工业成像等领域,它采用三阶RC积分环路滤波结构,提高了可达到的精度。针对环路延时降低系统稳定性的问题,在环路中引入半个采样周期的延时,以此提高调制器的精度;同时采用非回零的DAC结构来减小系统对时钟抖动的敏感度。通过结构的选取和非回零的DAC结构的使用,调制器对时钟抖动有很强的忍受能力。该Sig-ma-Delta ADC的带宽可以达到5 MHz,信噪比可达63.6 dB(10位),整个调制器在1.8 V的电压下,功耗仅为32 mW。

关键词:Sigma-Delta A/D转换器;连续时间调制器;高速低功耗ADC调制器;时钟抖动

O 引言

随着近些年来无线通信与视频技术的广泛应用,在这两个方向上主要使用Pipeline ADC和连续时间Sig-ma-Delta ADC(CTSD)。相比于Pi-peline ADC,连续时间Sigma-Delta ADC主要有以下几个优点:它有着更低的功耗,并且自身固有的抗混叠滤波功能,省去Pipeline ADC对前置滤波器的苛刻要求。由于这些优点,连续时间Sigma-Delta ADC还非常适合应用于医疗设备以及工业成像领域中。当然,连续时间Sigma-DeltaADC也有一定的缺点,主要是系统对时钟抖动非常敏感,并且非零环路延时对调制器信噪比有很大的影响。

在本文中,设计了一款三阶一位单环反馈结构的连续时间Sigma-Delta ADC,其带宽可达5 MHz,精度为10位,其中积分器采用RC积分器的形式。系统引入了半个周期的延时,提高了系统的稳定性,使得输入信号的最大幅度大幅提高,进一步增加了调制器转换信号的精度。同时,由于采用了新型的系统结构和非回零D/A转换器,使得调制器忍受时钟抖动的能力有了很大的提高,在与同类型的ADC设计的比较中达到了较高的水平。

1 系统结构设计

1.1 结构设计

由于连续时间Sigma-Delta ADC结构的系数不能像离散时间结构那样用电容的精确比值来实现,而是用电阻电容乘机的绝对值来实现,偏差较大。所以选择单环结构来实现系统的设计。为了实现5 MHz带宽和10位的精度,首先分析单环结构理论上的动态范围公式:

式中:L为系统阶数;N为量化位数;OSR为过采样率。

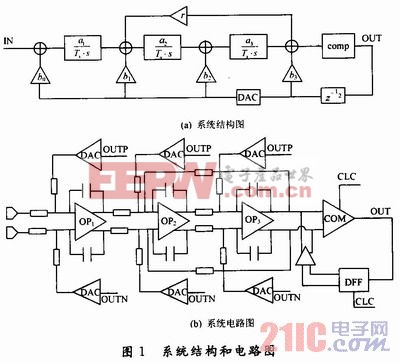

选取的系统结构见图1。对于单环结构来说,当系统的阶数超过三阶后,系统的稳定性会受到影响,从而导致可实现的动态范围降低。多位量化器需要校正电路,增加了电路的成本和面积,而一位量化器和D/A转换器具有天然的线性,减小了系统的非线性误差。故本文选择三阶一位单环结构。系统中加入一个很小的反馈系数 r,在系统带宽附近引入一个零点,可以将系统的信噪比提高大约8 dB。同时,调制器使用了半个周期的环路延时,大大提高了系统的稳定性。在设计时,利用图1中b3这一路的反馈来系统地补偿环路延时。结合系统对动态范围的要求,根据式(1),选择系统过采样率OSR=32。

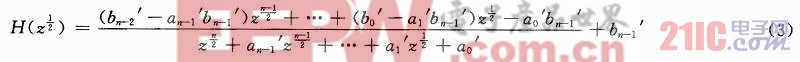

由于连续时间Sigma-Delta ADC缺少现成的设计工具,该设计采用的方法是先设计好离散时间的噪声传递函数NTF(z),根据式(2):

求出离散时间的环路传递函数H(z),再利用Matlab工具箱中的d2cm函数将H(z)转换为连续时间结构的环路传递函数H(s)。由于本结构的环路中加入了半个周期延时,故根据文献中的方法,将H(z)转换成等价的H()。因此,传递函数变为式(3):

式(3)中分离出来的系数bn-1’就是系统结构图1中反馈系数b3,通过对系数b3的选择可以精确地补偿系统中半个周期的延时。再利用d2cm函数将H()转换为H(s)。经过Sealing后,得到系统的系数为a1=O.3,a2=0.3,a3=0.5,b0=1,b1=1,b2=1,b3=O.9,r=-0.04。经过系统仿真可知,在处理5 MHz带宽内的信号时,系统的信噪比可达到72.3 dB。

1.2 时钟抖动

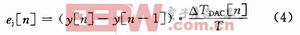

时钟抖动(clock jitter)对连续时间Sigma-DeltaADC的影响要比对离散时间Sigma-Delta ADC的影响大的多。时钟抖动对连续时间Sigm-aDelta ADC的影响主要体现在采样电路和DAC上。由于采样电路在滤波器之后,它产生的噪声被环路滤波三阶整形,而DAC产生的噪声有一部分直接加在输入信号上而未被整形,所以可以认为时钟抖动对信噪比的影响集中于DAC产生的噪声上。对于采用的非回零(NRZ)反馈DAC,可以把抖动噪声表示为式(4):

△TDAC[n]为采样时钟的抖动误差。将抖动噪声的方差表示为式(5):

其中dy=y[n]-y[n-1]。利用式(4)和(5),根据文献对系统受时钟抖动的影响进行建模仿真,可以得到,调制器在时钟抖动大约为30 ps时,SNR仍可保持在64 dB以上。

2 电路结构设计

在系统建模达到要求之后,采用图1(b)中的实际电路来实现系统的建模。电路包括三阶一位环路RC积分滤波结构、四输入一位量化器以及一位电压型NRZ DAC,采用RC积分滤波是因为这种滤波形式有更好的线性度和输出电压摆幅,可以实现更高的信噪比,同时为反馈DAC提供更好的虚拟地端。系统中采用由时钟控制的DFF实现所需的半个周期的延时。

2.1 运算放大器

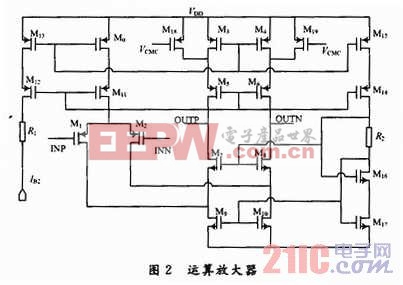

在环路设计中,运算放大器的设计是关键。对运算放大器进行建模,仿真得到在满足系统要达到的指标要求的情况下,运算放大器的DC Gain至少到达55 dB,增益带宽积GBW要达到2~3倍的采样频率,约为650~900 MHz。在设计中,选择电阻自偏置的折叠共源共栅放大器,如图2所示。

在设计中,VCMC为运放共模反馈电压,为电路提供稳定的共模电平。两个含有电阻支路为整体电路提供偏置,由IB2端输入基准电流。在CMOS标准工艺中,电阻的绝对值的大小变化很大。仿真显示,该设计中所采用的偏置电阻的值在8.4~15.6 kΩ之间变化时,偏置电路仍可为整体电路提供适当的偏压,运算放大器各指标所受的影响较小,仍可满足系统的要求。

第一级运算放大器没有受到噪声整形,所以对噪声的要求最为严格。选择PMOS差分对作为输入,以减少噪声。运放差分输入对的热噪声为:

ADC 相关文章:

- S3C2440A嵌入式手持终端电源管理系统设计(01-11)

- 基于CAN通信的电源监控系统的设计(04-06)

- 基于MSP430单片机的电源监控管理系统(04-20)

- 适用于全球交流电源的单节锂离子电池充电器设计(06-07)

- GPIB芯片TNT4882在多路程控电源中的应用(06-08)

- AD7656的原理及在继电保护产品中的应用(06-18)