提高有功模式效率以满足“能源之星”要求

电器设备在关断或没有运行主要功能时,其耗电量被称为待机功耗。一个设备一整年下来的耗电量可达约8600Wh,若待机功耗能减小1W,就相当于1美元/年的能源成本。尽管待机功耗看似微不足道,但如果考虑到家庭里所有电子设备的累积效应,这个数目就很可观了。美国家庭在这方面的能源成本每年就高达30亿美元左右,占美国住宅总用电量的近7%。

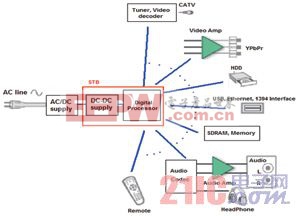

例如,从图1所示的典型机顶盒(STB),我们可以看到整个系统里有许多子电路。其中,AC/DC适配器采用AC电力线输入,然后输出一个DC电压,为红色框里的STB供电。STB还包含了一个DC/DC 功率部件,可把AC/DC电源输出的DC电压转换为众多更低的电压,供数字处理器和不同外设的连接所用。

图1 机顶盒(STB)的典型模块示意图

机顶盒系统

机顶盒系统包含有大量不同的子电路,其中每一个都可在待机模式下被关断,以降低总功耗。为了通过“能源之星”的认证,AC/DC适配器必须满足最低满载效率要求,而且空载功耗小于500mW。

STB要通过“能源之星”认证,必须确保睡眠模式下的功耗小于1W。

所有目标就是通过以下措施提高有功模式下的效率,降低待机功耗的。

1 关注架构级的改进,判断系统何时处于低功耗状态,采取措施提高效率。

2 提高元器件性能以优化最低功耗。

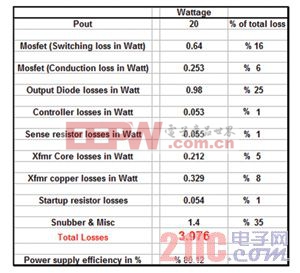

下面我们将从AC/DC部分开始分析,接下来是DC/DC和数字处理器部分。表1是一个采用普通输入,输出电压为32V,总输出功率为20W的典型反激式设计的损耗计算。该表表明,我们必须把关注焦点放在降低损耗上。

变压器损耗

从表1可看出,人们很容易忽略掉变压器损耗,而把注意力集中在缓冲电路、二极管以及MOSFET的损耗上。虽然所有这些损耗都非常重要,但缓冲电路损耗是由变压器的初级和次级绕组之间的松耦合(loose coupling)引起的,要降低缓冲电路损耗,实际上应该从变压器设计着手。通过优化绕组层的排列,可在初级和次级端之间形成更紧密的耦合,而且有效减少缓冲电路的能量泄漏,从而使互耦合 (mutual coupling)得以改进。

磁性元件是总电源损耗的主要原因,对于频率很低的满负载模式和PFM模式,采用损耗较低的材料,加之正确的绕组排列,可以同时降低磁芯损耗和AC损耗,最终提高电源效率。

在任何AC/DC反激式适配器设计中,由于加载的VIN很大,为了降低开关损耗,设计人员不得不采用较低的工作频率,这就给变压器带来了高压使用的问题。因此初级线圈需要很大的匝数,以使磁通量密度保持在其饱和点以下的某个合理水平。在空载条件下,另一个造成大量功耗的额外损耗是变压器的磁化电流。除了流入初级端的电流之外,不论连接负载与否,还有一个磁化电流或励磁电流(Imag)流入初级端,造成轻载或空载条件下的铜损耗。

图2 变压器泄漏和绕组模式

MOSFET损耗及封装

一般而言,性能更高的转换器设计可以推动MOSFET硅芯片及封装技术,实现尺寸更小、效率更高的产品。

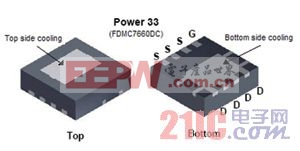

图3 Power 3356封装

低导通阻抗Rds(on)是实现满载条件下MOSFET传导损耗最小化的一个关键因素。由于封装键合引线与管脚的阻抗占据总阻抗的相当大部分,尤其是在Power56与Power33这样的新MOSFET设计中尤其明显,故需要特别关注使封装阻抗最小化。

相比其他类型的封装,采用Power 56/33这样带裸露铜引线框架技术和铝圆线互连的增强型封装,可以在占位面积更小的封装内获得出色的热性能和最佳的电气性能。比如,硅晶技术和封装技术两方面的进步(如双面冷却Power33封装),催生了出色的热性能,在电流高达20A的情况下,导通阻抗极低,仅仅为不到2mΩ,而尺寸仅3.3mm×3.3mm。

图4 先进的双面冷却power33封装

还有一点非常重要,就是不仅要考虑在满载条件下以更低的Rds(on)来获得更高的效率,还需考虑轻载条件下Rds(on)×QG(TOT)或品质因数(FOM)。

轻载条件下,Rds(on)没有那么重要,大部分损耗是由栅极驱动损耗造成,其为栅极电压平方的函数。

优化MOSFET的栅极电压也十分重要,因为若栅极电压增加,MOSFET的导通阻抗就会下降。不过,当栅极电压增加时,所需的栅极电荷Qg也随之增加。栅极驱动功率P=Qg·V·F,这里,Qg为栅极电荷,V为栅极电压,F是频率。

输出二极管损耗

2A/500mV标准肖特基二极管的传导损耗大约为1W。若正向电压降(VF)减小200mV为300mV,损耗可降至600mW,即功耗减小约400mW。对于电流较大的低压应用来说,用Rds(on)为10mΩ的同步MOSFET来代替肖特基二极管也是一种可选方案。

工作频率控制

另外还有一些能够减小控制器开关频率的技术,可用来降低待机模式下的功率半导体开关损耗。

其

收发器 相关文章:

- 基于CAN通信的电源监控系统的设计(04-06)

- 基于CAN总线的低压智能断路器的设计(04-06)

- GPIB芯片TNT4882在多路程控电源中的应用(06-08)

- 如何延长基于微控制器设计的电池寿命(06-24)

- 基于TPS2384的PSE设计与实现(07-12)

- 工频功率电源信号发生电路的实现(07-26)