用创新封装简化电源设计

工程师应对这种挑战的一个办法是利用在MOSFET硅技术和封装上的进步,这些进步能在更小尺寸的封装内实现更高的性能。通过这个趋势,我们可以发现,现在的封装已经从象SO-8这样的标准引线封装向采用底侧引出焊盘的功率封装转换。对于高电流应用,以前通常采用PowerPAK SO-8这样6mmx5mm的封装。但对于更低电流的应用,现在的趋势是采用3mmx3mm的功率封装,比如PowerPAK 1212-8。由于这种封装中的RDS(on) 已经足够低,在笔记本电脑的10A DC-DC应用中,这种封装已经广为使用。

虽然3mmx3mm的功率封装有助于大幅减少DC-DC电路所占的空间,还是有可能进一步减小空间需求,同时提高功率密度。实现这一点的办法之一是用组合了两个器件的封装替代分立式单沟道MOSFET。Dual SO-8功率MOSFET已经出现了很长时间,但是它们一般只能处理小于5A的负载电流,这对笔记本电脑和上网本中的5V和3.3V电压轨是足够了,但很显然,对于负载为10A和更高的系统来说,这个数值就太低了。

这就是为什么制造商正努力制造用于MOSFET的双片功率封装,因为这种封装能够实现比传统表面贴装更高的可能最大电流和更好的热性能。通过使用功率封装的基本形式,将两个单独的芯片组装在一个封装内,这种器件能够减小电源电路所需的占位空间。

一种称为PowerPAIR的封装形式的外形尺寸小于单芯片的6x5封装(PowerPAK SO-8),最大电流等级为15A。在笔记本电脑中,这样的负载电流一般要使用两片功率6x5封装,算上印制线和标识面积,以及放置两个器件后,所占面积至少是60mm2以上。这种功率双片封装的尺寸是6.0mmx3.7mm,所占用的电路板空间为22mm2。所占的电路板空间减少了63%,这对电源工程师来说是益处多多,因为留给他们设计电源电路的空间是越来越少。这种优点是传统SO-8双片封装类型所不具备的。

与两片功率6x5封装或两片SO-8封装相比,除了节省空间以外,这种器件还能够简化设计,对于那些正在使用两片功率3x3封装的工程师,这种器件还能再节省点空间。前面已经提到,在很多10A级的计算应用中,功率3x3封装已经成为一种趋势,因为这种封装比通常使用的标准SO-8封装尺寸更小,工作温度更低。功率双片封装能够很容易地用一个器件替代两片功率3x3封装,甚至还能再省出在PCB上布线和打标记的空间,如图1所示。因此,对于5A~15A的DC-DC应用,双片封装是一个很合理的设计,也是提高功率密度的一种方法。

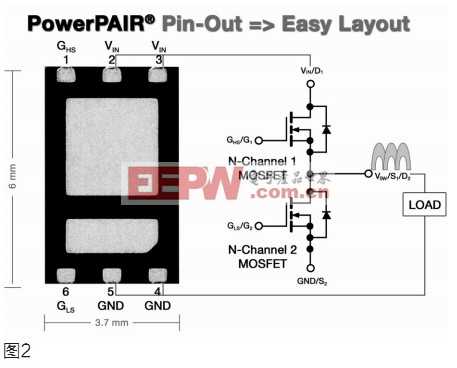

双片PowerPAIR功率封装使用对称结构,适用于DC-DC降压转换器。这种封装适合高边MOSFET的裸片和硅片降压转换器的低边MOSFET,并做了优化。这意味着,如图2所示,由于焊盘区的大小不一样,低边MOSFET的导通电阻比高边MOSFET的导通电阻更低。

事实上,低边MOSFET的导通电阻是器件的关键特性。即便封装尺寸变小了,这种封装还是能在4.5V电压下获得小于5mΩ最大RDS(on)等级。这有助于提高最大负载情况下的效率,尽管器件的尺寸不大,工作时的温度则更低。

这种器件的另一个优点是其布线。从图2可以看出,封装的引脚使其能很简单地集成进降压转换器设计中。更特别的是,输入安排在器件的一侧,输出在另一侧。引脚2和3与DC-DC电路的VIN匹配,也就是高边MOSFET的漏极。小焊盘也充当高标器件的漏极焊盘。更大的焊盘是电路的开关节点,高标MOSFET的源极和低边MOSFET的漏极从内部连到器件上。这是连接到电感器的节点。最后,接地是引脚4和5,这两个引脚是低边MOSFET的源极。引脚1和6是分别连到高边和低边MOSFET的栅极。这个布局很简单,减少了试图使用两个器件时布线出错的机会。将多个器件组合使用时需要额外使用PCB印制线,这种封装可减少与PCB印制线有关的寄生电感,

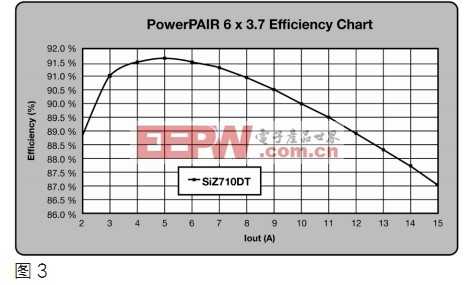

转向这种小尺寸功率双片封装的最后一个好处是所达到的效率水平能够有效提高功率密度。器件安装在单相降压转换器评估板上,具体条件如下:

VIN = 12 V, VOUT = 1.05 V, VDRIVE = 5.0V, fsw = 300 kHz, and IOUT max. = 15 A

效率是在整个负载范围内测量的。15A时,效率是87

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)

- 电源设计必看:开关电源设计经典问答(12-09)

- 电源设计小贴士:注意 SEPIC 耦合电感回路电流--第 2 部分(12-09)

- 电源设计小贴士:注意 SEPIC 耦合电感回路电流-第 1 部分(12-09)

- 电源设计控制的利弊权衡(12-09)