大功率高压高频变压器的设计

需要进一步提高功率或电压,无论采取何种模式,都有其固有的缺陷,实现起来也并不容易。特别是输出电压进一步升高的情况下,虽然可以通分层、分段、分包、分槽等绕制方式,但由于受到工艺制作的局限,使得如何控制分布参数尤其是分布电容将变的十分困难。

所以有没有一种既可以降低分布电容、又不增大漏感同时又适应工业化大批量生产的方法呢?所以在这里本着相互学习态度提出一种方案请大家相互探讨!

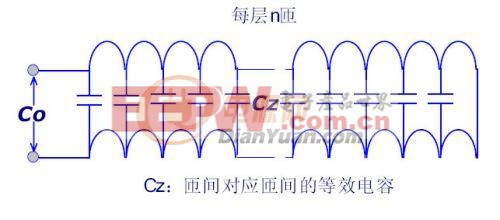

先说分布电容,如图所示

由图可见,基本上所有变压器都存在由两层之间的对应匝的电容并联而成的静态层间电容 Co,

而由分布电容的计算公式

不难发现Co是构成变压器分布电容大小的主要因素之一,如果可以将Co减小到

很低的程度,那么总的C不也很小了吗?也就是说,如果有一种绕制方法或则结构,首先使得Cz基本很小或非常小,那么Co、C不也就相应的降低很多了吗?

再说漏感

众所周知,环形变压器的漏感是最低的,原理这就不多说了。但是高压高频变压器几乎没有用环形铁芯来制作的,为什么呢?因为看上去似乎是不可实现的,例如首先初次级绝缘就好像做不到。你总不见得用高压导线去绕制吧?当然,如果体积可以宇宙大也不妨试试。

除此之外,高压变压器中最常用的就是C型或U型铁芯,这种铁芯用起来也方便,功率不够就多并几副,耐压不够就加大窗口,如此反复,不亦乐乎但是我觉得我们在这方面(大功率高压高频变压器)应该有点创新,四大发明都有了,这点还做不到吗?!!!

于是针对上面提出的几个关键点,我提出一种全新大功率高压高频变压器设计模式,具体下次再讲。

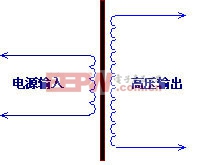

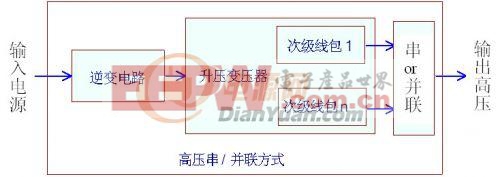

先上一个高压变压器原理图

也可以等效成下图:

这种方式类似于常见的分槽绕制

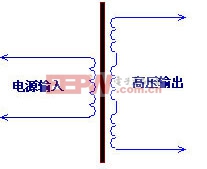

还有一种表示法

这个就像我们平时所说的分段绕制法,或者绕组电压叠加方式

这种方式,次级绕组是分为N个段,尽可能地降低分布电容,但是每段之间的层与层之间的分布电容还是不小。并且一旦出现由于负载短路、打火等原因而导致任何一个次级绕组的损坏,将会立即导致整个系统的失效。(转自电源网)

- 高压直流电源技术应用初见成效(12-09)

- 高压开关操作电源使用方法(12-08)

- 基于ISL8216M的高压大电流功率模块解决方案(12-08)

- 高压正弦波变频逆变电源的电路设计与实现(12-08)

- 可变高压电源 光电耦合器来凑热闹(12-07)

- 特高压直流输电知识普及问题综述(12-07)