同步整流技术及其在DC/DC变换器中的应用

摘要:同步整流技术是采用通态电阻极低的功率MOSFET来取代整流二极管,因此能大大降低整流器的损耗,提高DC/DC变换器的效率,满足低压、大电流整流的需要。首先介绍了同步整流的基本原理,然后重点阐述同步整流式DC/DC电源变换器的设计。

关键词:同步整流;磁复位;箝位电路;DC/DC变换器

1 同步整流技术概述

近年来随着电源技术的发展,同步整流技术正在向低电压、大电流输出的DC/DC变换器中迅速推广应用。DC/DC变换器的损耗主要由3部分组成:功率开关管的损耗,高频变压器的损耗,输出端整流管的损耗。在低电压、大电流输出的情况下,整流二极管的导通压降较高,输出端整流管的损耗尤为突出。快恢复二极管(FRD)或超快恢复二极管(SRD)可达1.0~1.2V,即使采用低压降的肖特基二极管(SBD),也会产生大约0.6V的压降,这就导致整流损耗增大,电源效率降低。举例说明,目前笔记本电脑普遍采用3.3V甚至1.8V或1.5V的供电电压,所消耗的电流可达20A。此时超快恢复二极管的整流损耗已接近甚至超过电源输出功率的50%。即使采用肖特基二极管,整流管上的损耗也会达到(18%~40%)PO,占电源总损耗的60%以上。因此,传统的二极管整流电路已无法满足实现低电压、大电流开关电源高效率及小体积的需要,成为制约DC/DC变换器提高效率的瓶颈。

同步整流是采用通态电阻极低的专用功率MOSFET,来取代整流二极管以降低整流损耗的一项新技术。它能大大提高DC/DC变换器的效率并且不存在由肖特基势垒电压而造成的死区电压。功率MOSFET属于电压控制型器件,它在导通时的伏安特性呈线性关系。用功率MOSFET做整流器时,要求栅极电压必须与被整流电压的相位保持同步才能完成整流功能,故称之为同步整流。

为满足高频、大容量同步整流电路的需要,近年来一些专用功率MOSFET不断问世,典型产品有FAIRCHILD公司生产的NDS8410型N沟道功率MOSFET,其通态电阻为0.015Ω。Philips公司生产的SI4800型功率MOSFET是采用TrenchMOSTM技术制成的,其通、断状态可用逻辑电平来控制,漏-源极通态电阻仅为0.0155Ω。IR公司生产的IRL3102(20V/61A)、IRL2203S(30V/116A)、IRL3803S(30V/100A)型功率MOSFET,它们的通态电阻分别为0.013Ω、0.007Ω和0.006Ω,在通过20A电流时的导通压降还不到0.3V。这些专用功率MOSFET的输入阻抗高,开关时间短,现已成为设计低电压、大电流功率变换器的首选整流器件。

最近,国外IC厂家还开发出同步整流集成电路(SRIC)。例如,IR公司最近推出的IR1176就是一种专门用于驱动N沟道功率MOSFET的高速CMOS控制器。IR1176可不依赖于初级侧拓扑而单独运行,并且不需要增加有源箝位(active clamp)、栅极驱动补偿等复杂电路。IR1176适用于输出电压在5V以下的大电流DC/DC变换器中的同步整流器,能大大简化并改善宽带网服务器中隔离式DC/DC变换器的设计。IR1176配上IRF7822型功率MOSFET,可提高变换器的效率。当输入电压为+48V,输出为+1.8V、40A时,DC/DC变换器的效率可达86%,输出为1.5V时的效率仍可达到85%。

2 同步整流的基本原理

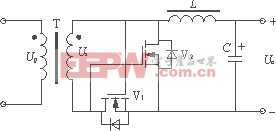

单端正激、隔离式降压同步整流器的基本原理如图1所示,V1及V2为功率MOSFET,在次级电压的正半周,V1导通,V2关断,V1起整流作用;在次级电压的负半周,V1关断,V2导通,V2起到续流作用。同步整流电路的功率损耗主要包括V1及V2的导通损耗及栅极驱动损耗。当开关频率低于1MHz时,导通损耗占主导地位;开关频率高于1MHz时,以栅极驱动损耗为主。

图1 单端降压式同步整流器的基本原理图

2.1 磁复位电路的设计

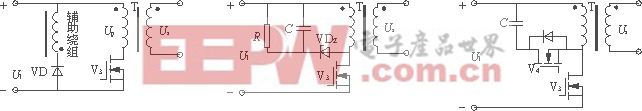

正激式DC/DC变换器的缺点是在功率管截止期间必须将高频变压器复位,以防止变压器磁芯饱和,因此,一般需要增加磁复位电路(亦称变压器复位电路)。图2示出单端降压式同步整流器常用的3种磁复位电路:辅助绕组复位电路,R,C,VDZ箝位电路,有源箝位电路。3种磁复位的方法各有优缺点:辅助绕组复位法会使变压器结构复杂化;R,C,VDZ箝位法属于无源箝位,其优点是磁复位电路简单,能吸收由高频变压器漏感而产生的尖峰电压,但箝位电路本身也要消耗磁场能量;有源箝位法在上述3种方法中的效率最高,但提高了电路的成本。

(a)辅助绕组复位电路 (b)R、C、VDZ箝位电路 (c)有源箝位电路

图2 单端降压式同步整流器常用的三种磁复位电路

磁复位要求漏极电压要高于输入电压,但要避免在磁复位过程中使DPA-Switch的漏极电压超过规定值,为此,可在次级整流管两端并联一个RS、CS网络,电路如图

- 大功率储能型有源箝位反激变换器的研究(02-28)

- 六种基本DC/DC变换器拓扑结构总结(12-12)

- 工程师自我养成之反激变换器控制环路仿真设计(12-09)

- 全桥变换器结构 软开关移相电源设计(12-07)

- 单级三相高频隔离AC/DC变换器设计(12-06)

- 一种电流温度稳定度小于1μA/℃的V/I变换器(05-27)