500兆/秒高速A/D系统的实现

摘要:介绍采样率为500兆/秒、采样精度为8bit的高速A/D系统的设计结构以及高速电路设计中的问题,最后还讨论了如何在Windows95下设计具有实时性要求的程序。

关键词:高速A/D变换 高速电路设计 Windows95 实时程序设计

在现代雷达系统、激光测距以及高能物理试验中往往产生宽带信号或者上升沿比较陡的信号(一般10ns左右)。若对此类信号进行数字化处理,要求A/D部分的采样率至少应该在200M/s以上。本文介绍的系统正是针对这样的要求而开发出来的。

1 系统结构

系统分为A/D转换和数据传输控制两大部分(图1)。数据传输控制部分作成PC机的插卡在计算机的PCI扩展插槽内,它的主要功能是将A/D采样得到的数据传递给计算机,同时产生相关的控制信号去控制整个系统;A/D转换部分由于受到电源和体积的影响单独作成一个模块置于计算机外部,其中关键的核心器件ADC采用的是MAXIM公司推出的MAX101A,它的最高采样率可达500兆/秒,采样精度为8bit。两部分之间的数据传递通过扁平电缆来完成。

2 A/D转换

2.1信号调理

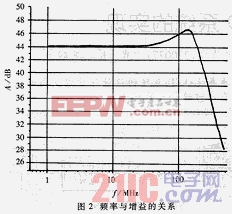

对于高速A/D采样电路来讲,前端调理电路显得尤为重要,不仅要有足够的带宽,而且还要将单端的输入信号变成差分信号提供给ADC,以减少偶次谐波的产生,同时本身的噪声也要很小,这样才不会对ADC的精度产生影响。考虑到上述因素,在前端部分采用了AD公司的AD8138作为缓冲放大器,它的性能指标为:-3dB带宽320MHz,输入噪声5nV/(根号Hz)。AD8138为表面封装器件,本身的体积非常小巧,使得ADC与信号输入点的距离可以很近,大大减少了外界噪声的影响。经测试,器件的模拟带宽为230MHz(图2)。

2.2 系统时钟的选择

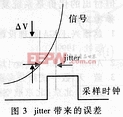

ADC芯片MAX101A要求的采样时钟为500MHz的ECL差分时钟。对于如此高速的时钟电路,孔径晃动(jitter)是选择时钟源的一个非常重要指标。Jitter是指时钟沿本身不稳定,在一定范围内晃动,时钟沿的晃动会带来采样点的不确定性,被采样信号的频率越高造成的误差就越大(图3)。经过调研,市场上有两种比较成熟的芯片可供选择。一是Motorola公司MC12439,另一个是Synergy公司的SY89424。MC12439可输出的频率是50~800MHz(Peak-to-Peak jitter 25ps 8δ),/TRK1 SY89424的最高输出频率为1GHz(Peak-to-Peak jitter 3δ)且两者的输出电平都为差分的PECL。虽然两种芯片给出的jitter相差不大,但实际上以上参数都是在输出时钟频率小于其最大输出频率一半的条件下给出的,也就是说此时的输出时钟是内部VCO的输出经过分频后得到的。如果输出时钟不经分频而直接输出,输出时钟的频率实际上是内部锁相环VCO频率的两倍,输出时钟的稳定性与VCO时钟的占空比有直接的关系。而VCO很难保证它的占空比总是50%,后以在这种情况输出时钟jitter将大大增加。鉴于上述原因,最终选择了Synergy公司的输出频率可达1GHz的SY89424。

2.3 特殊电平时钟的产生

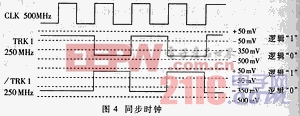

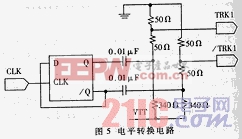

MAX101A芯片内部是由采样率为250兆/秒的完全独立的两个ADC拼在一起而得到的,从模拟信号输入、参考电压到数字信号输出都是完全分开的两部分。这样做给与用户很大的自由度,但同时也带来一个问题,那就是很难确定在每一次上电后究竟是哪一个ADC先输出,从而无法正确地进行数据锁存。MAX101A要求用户提供一个外加的控制信号TRK1和TRK1来确定两个ADC的先后顺序。它规定在系统采样时钟的下降沿到来时,如果TRK1为“1”,/TRK1为“0”则第一个ADC输出有效,反之则第二个ADC输出有效(图4)。这样的控制信号实现起来并不难,但MAX101A对TRK1和/TRK1的逻辑电平范围的规定是一个非常规的值,它规定输入电平在±50mV之间为逻辑“1”,在-350mV到-500mV之间为逻辑“0”。对于这样一种非标准的时钟电路,不可能用现成的芯片直接产生,为此在模拟伪真结果的基础上,采用了图5所示的电路来产生这样的时钟信号。D触发器将时钟信号二分频后经隔直电容送到电阻分压网络进行衰减,同时提供新的基准电平,这样原来的ECL信号(-900mV~-1800mV)就被转换成在0~-450mV之间的时钟信号,满足了MAX101A的要求。电容隔直方法在高速数字电路中应用十分广泛,应用这种方法可以很方便地将不同电平范围的信号(如ECL和PECL)进行相互转换而不需要额外的电路,使用起来相当方便。

2.4 高速数据的锁存

高速ADC的数据锁存在A/D系统里的设计一直都是一个难点,ADC的速度越高数据锁存的难度就越大。尽管MAX101A的数字输出已经分成了A、B两个端口,使每个数据通道的速率降为250Mbyte/s,但要将如此速度的数据准确无误的锁存下来还是相当困难的,必须进一步降低数据端口的输

- 基于PLC实现注塑机的电气控制(12-05)

- 电源模块均流的基本原理、实现方法及仿真应用(12-24)

- 工程师经验谈:如何实现一个驱动电路的三次设计?(01-18)

- 双输出 DC/DC 控制器结合了数字电源系统管理和模拟控制环路以实现 ±0.5% 的 Vout 准确度(11-07)

- 基于CAN总线的电流、电压变送器的设计与实现(10-26)

- 利用PSoC1实现基于WPC协议的电力发送器设计(09-19)