基于Ansoft仿真分析的SSN解决方案探讨

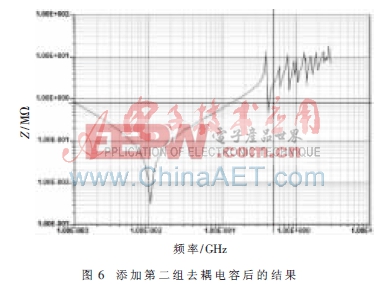

继续做谐振仿真,板子在f=0.257 GHz处发生谐振,再添加4个10 nF的电容矩阵(ESL=0.3 nH,ELR=0.03 Ω),此时的仿真参数如图6所示。

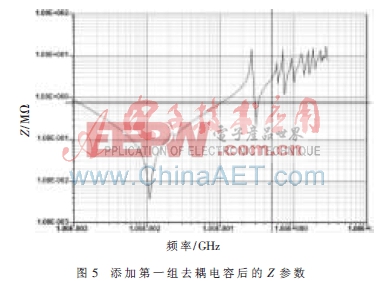

由图6可知,第一个尖峰值从图5中的180 MHz变到了图6中的400 MHz,然后在U17周围添加4个去耦电容,分别为0.3 nF、1 nF、3 nF、10 nF的电容矩阵(ESL=0.1 nH,ELR=0.01 Ω),为了使仿真与实际情况相符,还在板子最上端添加一个0.1 Ω的VRM等效电阻,此时的仿真Z参数如图7所示。由图7可知,添加去耦电容后,电源/地之间的阻抗变得非常小,在500 MHz频率内,基本低于0.825 Ω。由于容值更小的电容具有更小的ESL和ESR值,因此增加旁路电容的数量有助于提高其高频特性。

2 采用EBG(高阻抗电磁表面结构)抑制SSN

EBG结构是具有带阻特性的周期性结构,可以采用金属、铁磁或铁电物质植入基质材料,或者由各种合适材料周期性排列而成。采用EBG结构作为PCB衬底时,跨越几个EBG周期单元的电路元件将能实现滤波。利用EBG结构可以实现在微带电路衬底中集成具有很宽阻带的滤波器,当和其他电路元件有机地结合起来时,可节省电路空间。

采用EBG结构抑制SSN时,特别在高频时,效果比单纯加去耦电容好许多。因为频率的升高要求加入的去耦电容的数量随之变多,从而引起其他的一些效应。而采用EBG结构+去耦电容的方式则可以更有效地在更高频率范围上提供一个较大的禁带宽度,在最高频率下能尽量满足PDS的最小阻抗要求,从而减小SSN。

本文将对此单纯加去耦电容的PDS设计和采用8×8方形EBG结构加去耦电容PDS设计的仿真结果。第一组数据是两个80 mm×80 mm的平面电路板之间分别加入6×6电容矩阵和9×9电容矩阵,电容为10 nF,忽略其ESL和ESR。分别测试其Z参数。

结果表明6×6电容矩阵在频率为2 GHz以下其特性阻抗低于7 Ω,9×9电容矩阵在频率为3.7 GHz以下保持其特性阻抗低于7 Ω。

第二组数据采用前面分析8×8 EBG结构+6×6去耦电容矩阵和8×8改进EBG结构+6×6去耦电容矩阵两种结构,并仿真得出结果。

结果显示8×8 EBG+6×6去耦电容矩阵结构可以使特性阻抗在频率为3.4 GHz以下都保持低于7 Ω,而8×8改进EBG+6×6去耦电容矩阵结构则可以使特性阻抗在频率为4.2 GHz以下都保持低于7 Ω,结果表明采用EBG结构的PDS设计比传统单纯加去耦电容更具有优势。

参考文献

[1] CHEN Guang, KATHLEEN M, JOHN P.The applications of EBG structures in power/ground plane pair SSN suppression[J].IEEE Microwave and Wireless Components Letters, 2004,15(3).

[2] HOWARD J, MARTIN G.High-speed digital design[M]. Prentice Hall PTR, 1993.

[3] BOGATIN E.Signal integrity-simplified[M].Prentice Hall PTR, 2003.

[4] PART M D,PANT P,WILLS D S.On-chip decoupling capacitor optimization using architectural level prediction[J]. IEEE Transactions on Very Large Scale Integration(VLSI) Systems, 2002(2):319-326.

[5] KOZHAYA J N,NASSIF S R,NAJM F N.A multigrid-like technique for power grid analysis[J].IEEE Trans. on CAD of integrated circuits and systems, 2002,21(10):1148-1160.

解决方案 探讨 SSN 分析 Ansoft 仿真 基于 相关文章:

- 大联大控股世平推出高性能电机控制解决方案(04-11)

- “可持续性”模块电源解决方案(01-26)

- 反激式电源中的常见噪声来源及可操作的解决方案(12-27)

- 基于Fairchild和NXP产品的电源解决方案(12-10)

- 工业交换机行业电源解决方案(11-12)

- 电源测试一体化解决方案(09-28)