基于Cadence_Allegro的高速PCB设计信号完整性分析与仿真

时间:06-29

来源:互联网

点击:

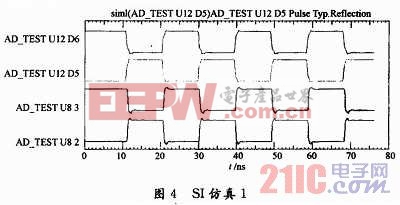

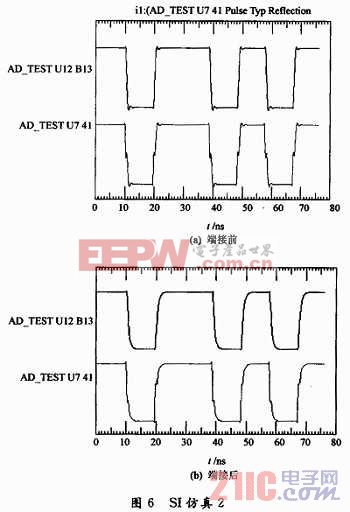

2.2 对AD时钟信号的反射仿真与分析 由图4可知,由于合理的布局布线,高频差分时钟信号经过传输线时信号发生的变化极小,保持了较好的质量。 如图6所示,采用端接电阻后数据波形质量明显提升,端接能有效解决阻抗不匹配所引起的反射问题。

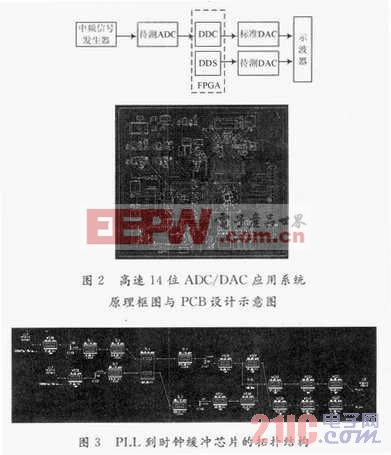

仿真主要基于IBIS模型,它是用于描述I/O缓冲信息特性的模型,它可以将一个输出输入端口的行为描述分解为一系列的简单的功能模块,由这些简单的功能模块就可以建立起完整的IBIS模型。本应用系统时钟是由FPGA软件倍频后经由时钟缓冲器件分配到ADC,DAC网络的。提取的由FPGA锁相环到时钟缓冲芯片的拓扑结构如图3所示。

对其SI仿真如图4所示。

2.3 对AD数据信号的仿真分析

对ADC通道A第0位的SI仿真如图5所示。

Cadence_Allegro软件中的Specctraquest和Sigxp组件工具,为高速PCB的设计与仿真提供了强有力的支撑,包括仿真模型验证、拓扑分析、布线前与布线后仿真、约束条件的设置、PCB布局布线等硬件环节,通过仿真结果可促使设计者较好地把握信号完整性问题,优化设计,提高高速PCB设计的一次成功率,较好地应对高速设计所面临的挑战。

完整性 分析 仿真 信号 设计 Cadence_Allegro 高速 PCB 相关文章:

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 抑制SSN的新型内插L-EBG结构(06-28)

- 高速电路之信号回流路径分析(04-17)

- 电源完整性设计2(02-07)

- 电源完整性设计1(02-07)

- 电源完整性设计中电源系统噪声余量分析(12-21)