基于PLL技术的电源管理设计

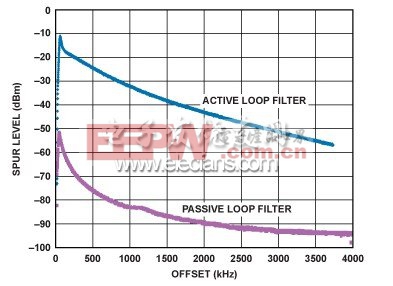

该设计选择噪声滤波器选项,并将VOUT纹波场设定为最小值。高压电荷泵的功耗为2 mA(最大值),因此OUT 为10 mA以提供裕量。该设计使用20 kHz的PLL环路带宽,通过ADF4150HV评估板进行测试。根据图7,可能获得约70dB的PSR.由于PSR极佳,此设置未在VCO输出端呈现明显的开关杂散( –110 dBm),即使是在省去噪声滤波器时。 图8.ADP1613升压转换器EXCEL设计工具 作为最终实验,将高压电荷泵的PSR与有源滤波器(目前用于产生高VCO调谐电压的最常见拓扑结构)进行比较。为执行测量,使用无源环路滤波器将幅度为1 V p-p的交流信号注入ADF4150HV的电荷泵电源(VP)与图6的测量设置相同。后以有源滤波器代替相等带宽的无源滤波器,重复相同的测量。所用的有源滤波器为CPA_PPFFBP1型,如ADIsimPLL所述(图9)。 图9.ADlsimPLL中CPA_PPFFBP1滤波器设计的屏幕视图 为提供公平的比较,电荷泵和运算放大器电源引脚上的去耦相同,即10 μF、10 nF和10 pF电容并联。测量结果显示于图10中:与有源滤波器相比,高压电荷泵的开关杂散水平降低了40 dB至45 dB.利用高压电荷泵改善的杂散水平部分可解释为通过有源滤波器看到的环路滤波器衰减更小,其中注入的纹波在第一极点之后,而在无源滤波器中注入的纹波位于输入端 图10.有源环路滤波器与高压无源滤波器的电源纹波电平 最后一点:图1所示的第三电源电轨(分压器电源,AVDD/DVDD-与VCO和电荷泵电源相比具有较宽松的电源要求,因为PLL(AVDD)的RF部分通常是具有稳定带隙参考偏置电压的双极性ECL逻辑级,所以相对不受电源影响。另外,数字CMOS模块本质上对电源噪声具有更强的抵抗力。因此,建议选择(DVDD)能够满足此电轨电压和电流要求的中等性能LDO,并在所有电源引脚附近充分去耦;通常100 nF和10 pF并联就够了。 结束语 以上已讨论主要PLL模块的电源管理要求,并针对VCO和电荷泵电源推算出规格。ADI公司为电源管理和PLL IC提供多种设计支持工具,包括参考电路和解决方案,还有各种仿真工具,如ADIsimPLL和 ADIsimPower. 了解电源噪声和纹波对PLL性能的影响后,设计人员可以回头推算电源管理模块的规格,进而实现性能最佳的PLL设计。

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 高效地驱动LED(04-23)

- 电源SOC:或许好用的“疯狂”创意(07-24)

- 实现智能太阳能管理的微型逆变器应运而生(05-06)