最新全能数控电源IC-ADP1043A(五)

摘要:随着数字技术的发展和成熟,电源产品更多地向数字化方向发展。采用数字技术可减小电源高频谐波干扰和非线性失真,同时便于CPU数字化控制。文中重点介绍了ADP1043A的功能、原理及具体应用细节。ADP1043A的创新架构能支持多种拓扑结构,其图形化的操作界面、丰富的监控和管理功能,非常方便技术人员操作,也改变了以往对数字电源的认识。

关键词:ADP1043A;EEPROM;OrFET控制;同步整流 (上接第8期)

3.13 恒流工作模式

ADP1043A可调成恒流模式工作,进入恒流模式工作,要在CS2精确OCP设置的10%电流一下,再次电流下部分工作正常,用输出电压作为反馈信号形成闭环工作。

当ADP1043A达到恒流模式阈值时,设置一个标志,CS2电流达到是用替代输出电压作为反馈信号达到闭环工作,输出电压线性下斜到60%的正常值,岁负载电阻减小而减小,以保证电流恒定。

当控制环达到VOUT的60%,部分增益用输出电压到闭环,但减小水平(正常值的60%),如果负载电阻继续减小,电流可能再次上升,知道CS2

的OCP水平,但电压保持限制在60%的正常值,如图15所示。UVP或CS2的OCP标志可用于调节关断功能。

3.14 过压保护(OVP)

ADP1043A有两个OVP电路,如果输出电压在VS1,VS2,VS3端超出其预先调节的阈值,则OVP标志及设置,响应此标志可以调节,VS1有一个OVP电路,VS2和VS3可以均恒其他OVP电路,OVP电路可用不同OVP阈值调整,见寄存器0*32和0*33,设置OVP阈值计算下式给出:

VSx OVP=[(89+VS1_OVP_Setting)/128]×1.55V

例子,在VS1 OVP设置为10,则

VS1 OVP=[(89+10)/128]×1.55V=1.2V

3.15 欠压保护(UVP)

如果在VS1端检测的电压低于调定的UVP阈值,则UVP标志即设置出,例外包括在启动期间ACSNS没在限制之内,响应UVP的条件可以调节。

3.16 AC检测(ACSNS)

ACSNS电路执行多个监视功能,它间接由初级测输入电压状态决定,如在同步整流级处,监视开关波形一样,同步整流级接到这一端,也是通过一个外部电阻分压器网络。

ACSNS电路在ADP1043A内部有一个比较器,检测0.45V的信号,或大于每个开关周期,例如,如果开关频率设置在200kHz,开关周期即为5μs,比较器时间输出也设在5μs,一边匹配开关周期,如果比较器没有处罚(在5μs内),则ACSNS标志设置出。

3.17 伏·秒平衡

工作在全桥拓扑时,主变压器中,有一个致力于保持伏·秒平衡电路。这意味着一个直流大容积是不必要的。电路监视流过全桥两个对半的直流电流,并储存此信息,它补偿PWM驱动信号,以确保相同的电流流过半桥路,需要通过CS1的输入几个开关周期,才能有效的工作,伏·秒平衡在80ns内调制于OUTB和OUTD端注意PWM驱动信号的补偿,仅在t4(OUTB)和t8(OUTD)处执行,因此,它需要用此端去调制PWM信号,以保证正常工作。

SR1,SR2的上升沿(t9和t11)也由设置的伏·秒电路调制来决定,SR1上升沿(t9)调制根据OUTB的下降沿(t4),SR2上升沿(t11)的调制根据OUTD(t8)的下降沿调制。

还要注意ADP1043A假设CS1电流脉冲信号,在每个周期中第一次见到是相对OUTB,第二个电流脉冲是相对OUTD。如果第一个电流脉冲信号小于二个。OUTB增加而OUTD减小,如果第一个电流脉冲信号大于第二个,则OUTB则减小而OUTD则增加。

3.18 负载线

ADP1043A能够选择介入数字负载到电源中,这个选择可由负载线阻抗寄存器调节(0*36),这个特点可用于先进的电流均衡技术。用这项故障功能,负载线可被禁止,负载线数字式插入,它的斜率可以调节,它用从CS2电流读出取样,并可调节响应的输出电压,可选择51.5mΩ的负载线,如图16所示的负载线的应用结果,评估板用10mΩ的检测电阻。

ADP1043A允许完整地进入电源校准和数字式调节,它能校准各项诸如输出电压,用加入检测电阻来调节偏差,如同自己内部电路一样,该部分在工厂中调节,但可以在用户处再次用外部元件调节。

ADP1043A允许用户足够能力去校准,用外部元件调整偏差,最高0.5%的精度,如果ADP1043A设在生产环境中校准,推荐用0.1%精度的元件去调节CS1,CS2,VS1,VS2,VS3+和VS3-,以满足数据表的规范。

4.1 CS1调节

(1)使用一个DC信号

已知电压VX加到CS1端,CS1的ADC将输出一个数字编码到VX/337mV,CS1增益调节寄存器(0*21)调节知道CS1的ADC值达到正确的数字码。

(2)使用一个AC信号

一个已知电流(IX)加到PSU端输入,该电流通过一个电流互感器,一个二极管整流器和一只外部电阻RCS1去改变电流信息,以改变电压VX这个电压送进CS1端,电压VX计算如下

VX=IX×(n2/n1)xRCS1

此处n2/n1为互感器匝比。

CS1的ADC将输出一个数字码,它等于VX/337μV。CS1增益调节寄存器(0*1)是一个可调整的,知道CS1的ADC在寄存器中的值达到正确的数码。

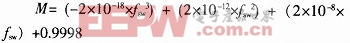

如同在CS1部分描述的,CS1的ADC有一个频率的响应,为实现更精确的调整,下面的乘法因子M将用上

此处fSW为开关频率。

4.2 CS2调节

CS2调节必须补偿失调及增益误差,失调误差需要模拟调节和数字调节两者,CS2的ADC范围设在0V开始,而是-25mV到性能回复的电流保护OrFET的反转处。因此,在CS2输入处有-25mV。ADC码将读出0。在CS2输入有0mV。ADC码将读到100,根据这个理由,模拟失调的调节要先执行知道CS2读出等于100(没有0),据此,还需要数字调节。

4.3 CS2的失调调节

CS2失调调节是很重要的,如下面所描述的。

(1)设置正常的全比例寄存器0*23中的检测电阻电压降。

(2)设置高边或低边的电流检测于寄存器0*24中。

(3)失调误差可以用外部偏置电阻和北部电流源插入,在检测电阻中,无负载电流,调节CS2,失调值知道CS2在寄存器0*18中的值尽可能地接近100。

(4)调节CS2的数字调节寄存器(0*25)直到CS2在寄存器0*18中达到0。失调调节现在执行。ADC码达到0时就没有电流流过检测电阻。

4.4 CS2的增益调节

在执行失调调节中,执行增益调节可以移去任何失衡,它由检测电阻的误差代替。

(1)加入已知电流IOUT到检测电阻。

(2)调节CS2增益调节值,知道CS2在寄存器0*18中的值达到由下式计算出的值。

CS2 Value=IOUT×2457×(RSENSE/FS)

此处FS全比例电压降。

例如,IOUT=4.64A,RSENSE=20mΩ,FS=150mV。

CS2 Value=(4.64A×2457)×(20mΩ/150mV)

CS2 Value=1520 decimal

CS2电路现已调节,在电流检测调节执行之后,OCP限流点将设在规范值处。

4.5 电压校准和调节

电压检测输入最佳化为检测信号在1V,且没有大于1.5V时,在12V系统中,需要一个12:1的电阻分压器去使12V信号降到1.5V一下,推荐电源输出电压减小到1V时有最好的性能,电阻分压器会加入误差,它需要调节,ADP1043A有足够的调节范围去调节由电阻带入的输出误差,可达到0.5%或更好,ADC的输出数字码为2643, (0*A53)此时在它的输入端超出1V。

4.6 输出电压设置(VS3+,VS3-的调节)

VS3输入需要增益调节,零电源空载下使能,电源输出电压由VS3的电阻分压器给出VS3+为1V,VS3-为1V。VS3调节寄存器改变直到寄存器中的VS3,寄存器的值达到2643(0*A53),这个步骤在任何其他调整前就要做好。

4.7 VS1调节

VS1输入需要增益调节,令电源空载下使能,VS1电压由VS1电阻分压器给出到1V,VS1端处,VS1调节寄存器(0*38)改变,知道寄存器中的VS1值达到2643 (0*A53)。

4.8 VS2调节

VS2输入需要增益调节,令电源空载下使能,VS2电压由VS2电阻风雅其给出到1V,于VS2端处,VS2调节寄存器(0*39)改变知道寄存器中的VS2值达到2643(0*A53)。

4.9 RTD/OTP TRIM

一个100kΩ的NTC热敏电阻用于ADP1043A。在PSU调节端用下面的过程。

(1)加热热敏电阻或PSU到已知温度,其结果在一个OTP阈值处。

(2)调节温度增益调节寄存器(0*2B)给出校正温度,此时的读数。

(3)调节OTP阈值寄存器,直到OTP标识设置出来。

(4)这个过程实现了最精确的OTP,因为它用了ADP1043A及热敏电阻的一个一个变化的计数。

4.10 PCB布局的考虑

这部分说明最实际的问题,它将跟随ADP1043A确保其最优性能,通常所有元件都紧靠ADP1043A来放置。

几个送入ADP1043A的信号端都是敏感的,因此,要极其小心的掌握并解决这部分布局,随后沿着IC正确清晰的,用最短的引线处理它,AD公司还推荐密封此IC,加上树脂,以保护它,此后确保任何杂质都不能污染此IC。

CS2+,CS2-:从检测电阻到ADP1043A的轨迹的路线要安置或并联模式。轨迹要紧靠在一起,原理开关结点。

VS3+,VS3-:从遥远电压检测点到ADP1043A的轨迹路线也要并行并且紧靠在一起,互相并行紧靠,并原理开关结点。

VDD:放置去耦电容尽可能靠近IC,一个100nF瓷介电容从VDD到AGND。

SDA和SCL:这两个引线也要并行互相紧靠,并远离开关结点。

CS1:从电流互感器到ADP1043A的引线,也要互相并行,要紧靠在一起,并原理开关结点。

暴露的焊接点:

在ADP1043A下面暴露的焊接点,要焊接到PCB低线布局面。

VCORE:放置100nF电容紧靠此端子及相关部分。

RES:放置49.9kΩ电阻紧靠此端子及相关部分。

RTD:从热敏电阻到ADP1043A要用一轨迹接入,放置的热敏电阻要紧靠电源中最热的元件。

AGND:建立一个AGND接地布局,并为单点结构,然后接到功率地PGND。 (未完待续)

IC-ADP1043A 电源 数控 全能 最新 相关文章:

- 最新全能数控电源IC-ADP1043A(六)(02-07)

- 最新全能数控电源IC-ADP1043A(二)(08-10)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)

- 负载点降压稳压器及其稳定性检查方法(07-19)

- 电源设计小贴士 3:阻尼输入滤波器(第一部分)(01-16)