SoC 设计中的时钟低功耗技术

时间:12-24

来源:互联网

点击:

时钟树规模为目标,进行低功耗时钟树综合是以增加一定的时钟偏差为代价的。

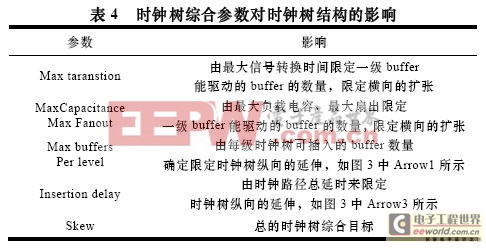

后端工具在进行时钟树综合时,能通过综合参数对时钟树结构进行约束,见表4。

对rsthu1 的快速时钟HCLK 进行时钟树综合时,采用以降低时钟树规模为目标的低功耗时钟树综合,结果如表5 所示。分别加大最大扇出,减小路径总延时和每一级缓冲器数量上限。加大最大扇出后,时钟树规模减小了20.21%,而时钟偏差只增加了0.023 ns,因此,由减小时钟树规模而带来的偏差结果的变差是可以接受的。

5 结束语

目前已有很多时钟低功耗技术,在SoC 芯片的设计中可以进一步降低由时钟网络引起的功耗。在以后的研究工作中,需要进行更广泛而深入的探索。

- 功率与控制的结合使LED照明方案灵活、简便(10-20)

- 以89C51单片机为控制核心的开关电源优化设计(07-25)

- 用于低功耗SoC设计的自适应电压调节技术(07-28)

- 满足多媒体处理器动态需求的电源管理技术(08-12)

- 嵌入式Linux的动态电源管理技术(09-03)

- Power Architecture许可开放飞思卡尔e200系列内核助力SoC设计(09-17)