SoC 设计中的时钟低功耗技术

1 概述

SoC 芯片设计的复杂度日益增加,其内部时钟设计越来越复杂,一个SoC 芯片内部通常存在若干个时钟域,由时钟网络引起的系统动态功耗成为近年来的研究热点。时钟网络引起的系统动态功耗分为2 个方面:(1)由于时钟网络的作用是为芯片内部所有时序单元提供时钟信号,因此时钟频率的快慢决定了时序单元和与之相连的逻辑单元的动态功耗,关断时钟将消除电路的动态功耗。(2)时钟网络自身的特点将导致巨大动态功耗的产生:1)时钟网络是芯片内规模最大的互连线网络,其负载巨大,负载来自因为互连线电容和平衡时钟树的偏差而插入的大量延时单元;2)时钟网络是芯片内翻转率最高的互连线网络,翻转率的高低直接决定了互连线动态功耗和互连线驱动的标准单元的动态功耗。

针对由时钟网络引起的2 种系统动态功耗,本文研究并实现3 种时钟低功耗技术。

2 动态时钟管理

一颗SoC 芯片的工作状态变化很大,一些应用需要用到芯片内部的所有模块,而另一些应用只要用到部分模块;在某些应用中,芯片需要全速运行,而在其他应用中,则可以运行在很低的工作频率[1]。综合以上2 点,动态管理芯片的时钟可以分为2 个方面:动态地开关芯片内部模块的时钟,动态地配置芯片内部模块的时钟频率。

本文以音视频解码SoC 芯片——rsthu1 为例,介绍在系统级设计时采用的动态时钟管理技术。

为了实现rsthu1 的动态时钟管理,在芯片系统级设计时定义了4 种工作模式,见表1,其中,实心圆表示开启此模块;空心圆表示关闭此模块。

当芯片工作在正常模式时,采用高速时钟HCLK 供给Risc0, Risc1, Decoder, BE(Bit Engine)这4 个系统内的主要模块,此时系统全速运行,进行音视频解码。当芯片工作在低速模式时,采用低速时钟VCLK 供给上述4 个模块,此时系统可以运行简单的应用程序,保证了系统的持续工作,且降低了时钟频率,即降低了系统的动态功耗。当芯片工作在闲置模式时,只保留操作系统的运行,采用低速时钟VCLK 供给Risc0,关断其余模块的时钟供给,消除了除Risc0 以外其余模块产生的动态功耗。当芯片工作在睡眠模式时,关断所有模块的时钟供给,消除系统不工作时产生的动态功耗。

采用Synopsys 公司的功耗分析工具Prime Power,在RTL级基于4 种工作模式的仿真波形进行功耗分析,结果见表2。

可以看出,在系统级设计时采用动态时钟管理技术后,正常、低速、闲置、睡眠4 个工作模式下,系统动态功耗逐级递减,功耗优化效果明显。

3 门控时钟

RTL 代码中经常会出现以下语句:

@posedge (CLK)

begin

if (EN == 1)

Data_out = Data_in;

end

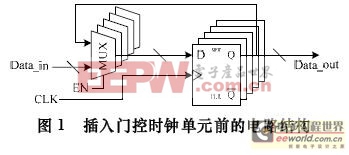

如果直接对上述代码进行逻辑综合将生成如图1 所示的电路结构。控制寄存器状态更新的控制信号被置于寄存器的输入端之前,通过控制是否接收新数据来控制寄存器状态是否更新。在该结构的电路中,寄存器状态不更新时的寄存器时钟端仍然在不停翻转,会浪费系统动态功耗。

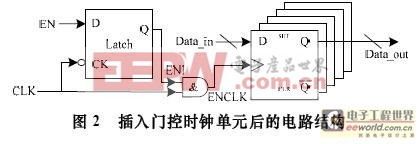

采用图2 的结构,将控制信号置于寄存器的时钟端之前,通过控制寄存器是否翻转来控制寄存器状态是否更新。与图1 的电路结构相比,图2 的电路结构在寄存器状态不进行更新时,时钟信号将不翻转,消除了由此带来的系统动态功耗的浪费。由于多个MUX 被替换为一个门控时钟单元,因此进一步降低了功耗。

门控时钟单元可以通过Synopsys 公司的功耗优化工具Power Compiler 在逻辑综合时插入,其优点在于[3]:(1)不需要对RTL 级代码进行修改,Power Compiler 将自动检测出RTL 代码中可以插入门控时钟的语句;(2)门控时钟单元将在逻辑综合时自动插入门级网单中。

采用Power Compiler 对rsthu1 进行门控时钟综合,并采用Prime Power 进行功耗分析,结果如表3 所示。可以看出,在逻辑综合时采用门控时钟技术,总功耗下降了34.52%,功耗优化效果明显。

4 低功耗时钟树综合

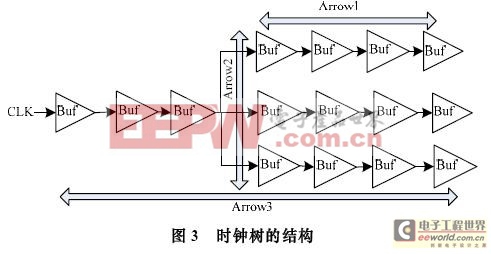

观察时钟树的生长过程,可以发现时钟树的生长分为横向扩张和纵向延伸,如图3 所示,其中,Arrow1 和Arrow3为纵向延伸;Arrow2 为横向扩张。

普通的时钟树综合以降低时钟偏差为目标,加大纵向延伸,减小横向扩张,将投入较多buffer,更细粒度地调整每条时钟路径的延时,从而得到较小时钟偏差。上述方式以增大时钟树规模为代价,它综合得到的时钟树如图4(a)所示。

出于功耗的考虑,希望能减小时钟树的规模。通过减小时钟树纵向延伸,加大横向扩张可以有效减小时钟树的规模,如图4(b)所示。但由于buffer 数量的减少,较之纵深结构的时钟树,扁平结构的时钟树将粗粒度地调整每条时钟路径的延时,得到的时钟偏差较大。可见,以降低

- 功率与控制的结合使LED照明方案灵活、简便(10-20)

- 以89C51单片机为控制核心的开关电源优化设计(07-25)

- 用于低功耗SoC设计的自适应电压调节技术(07-28)

- 满足多媒体处理器动态需求的电源管理技术(08-12)

- 嵌入式Linux的动态电源管理技术(09-03)

- Power Architecture许可开放飞思卡尔e200系列内核助力SoC设计(09-17)