一种新型高线性度采样开关的设计

摘要 设计了一种应用于流水线ADC中的新型高线性度采样开关,该开关采用比较器、反相器链、CMOS对管开关,自举电容等实现,具有较高的线性度。其基本原理为:使MOS管栅极电压实时跟随输入电压,保证其差值恒定,从而实现整体采样保持电路较高的无杂散动态范围。通过Flip-around型采样保持电路进行验证,其无杂散动态范围可达91dB,满足设计要求。

关键词 采样开关;栅源跟随;高线性度

在ADC转换器的设计和应用中尤其在音频、视频系统中,谐波失真是要考虑的因素,对于传统ADC的采样开关而言,CMOS对管,用MOS管作为开关使用时是不分漏源级的,当实际采样到的信号不断变化时,其源级也无法确定,这就导致无法通过将源级和衬底相连的方式消除衬底偏置效应,从而导致开关的非线性较大,这对ADC的非线性影响也较大。

针对此问题,基于MOS管栅源级电压跟随技术,设计了一种新型高精度采样开关,能有效减小MOS管的衬底偏置效应,可广泛应用于流水线ADC,逐次逼近ADC等模数转换器和各种采样系统中,具备良好的线性度。

1 采样开关的设计

1.1 工作原理

本项目设计14位100 MHz采样速率的高精度采样保持电路,考虑到实际电路中的寄生非理想特性,ADc中采样保持电路的谐波失真主要由采样开关的导通等效电阻,沟道电荷注入效应以及输入寄生电容等因素影响。为确保一定的线性度和输入信号带宽,文中对传统CMOS对管开关电路进行了优化和重新设计,确保满足系统高线性度的要求。

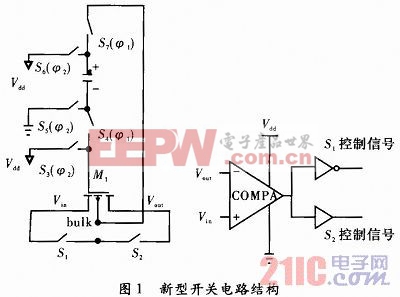

如图1所示,设计的新型开关主要由基本CMOS对管开关,比较器和反相器链组成。由于要实时判断哪个端口为源级和漏级,因此加入了2个衬底选择开关S1和S2,由互补开关组成。采用比较器触发S1和S2使衬底能够连接到实时变化的源端。在采样开关M1管导通的状态,衬底确保能够只连接到一个端口。采用直接连接源端和衬底的结构,使M1管的偏衬效应得以消除,使其具有较小的非线性和较大的输入摆幅。下面讨论两种情况,分别分析M1管分别导通和关断时的工作原理。

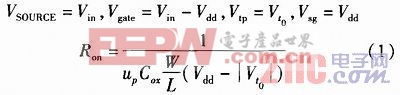

在关断时(S6,S5和S3打开),自举电容会被充电到Vdd。在导通时(S7和S4打开),当VinVout,即比较器输出为低电平时S1打开,直接连接输入端和衬底。采样开关M1的栅极电压此时等于Vin-Vdd,源栅电压Vsg和源衬电压Vsb分别接到电源电压Vdd和0。根据MOS管基本公式可得

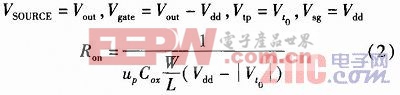

当Vin>Vout时,情况和前面正相反。开关S2由比较器作用以连接输出端和衬底,对应此时真正的源端是输入端。采样开关M1的栅极电压变成Vout-Vdd,同时源端电压是Vout。此时Vsg仍然准确地为Vdd不变,阈值电压同样不变。与式(1)类似,同理可得

在导通状态,当输入和输出之间的电压差变为0时,比较器输出低电平,此时驱动S1再次打开。

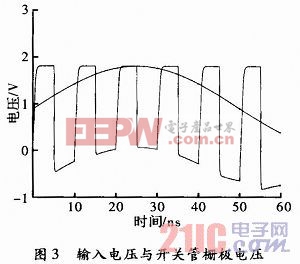

图2为设计中的实际电路架构,图3为输入电压与开关管栅极电压的变化曲线,可看到当输入源(漏)级正弦信号变化时,采样到的栅极电压跟随输入信号,即源栅电压Vsg为恒定常数,因此衬底效应被抑制,开关的线性度有了较大提高。

1.2 开关中比较器的设计

由于要求达到14位的采样精度,从而导致比较器的精度必须达到16位以上。运放型比较器的精度公式为

式(3)中AV为比较器增益;VOH,VOL分别表示输出高低电平,较高精度需保证一定的增益。

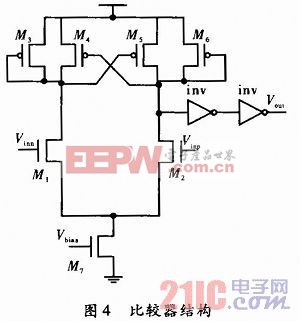

比较器采用MOS二极管连接类型的负载,分别等效为正、负电阻,同时输出串联两个反相器以增加后级驱动能力,如图4所示。

采样时的非理想效应如电荷注入等可等效看作是输入信号的共模噪声,会严重地影响采样的线性度,因此采用输入输出全差分结构来抑制。为达到一定的增益要求,可采用电流源负载,但需要单独的偏置电路产生偏置电压,增加了复杂性。MOS二极管连接形式的负载对增益和运放带宽的影响比较折中,因此可用作负载。由小信号等效分析可得,该运放的增益由式(4)给出。

其中,gM1,gM3和gM4分别对应输入管M1和负载管M3和M4的跨导参数。由传统运放理论可知:要增加增益需增大输入对管的跨导,但由于电压型运放的增益带宽积为固定常数,因此一味地增加输入管跨导会导致带宽变小,从而影响速度。由式(4)可知,设计中只要gM3与gM4差值较小,gM1不需要过大,运放就可达到较高的增益,故设计中可采用较小的晶体管来抑制增益带宽积为固定值的不利影响,同时较小的晶体管尺寸可以有效降低其寄生电容效应,从而减小输入寄生电容对采样速度和精度的影响。

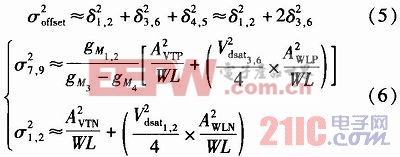

非理想情况下,由于工艺偏差等因素造成比较器随机产生一定的失调电压,会影响比较器可比较的最小精度。从统计学角度分析,其服从均值为零的高斯分布,比较器的失调电压近似为

其中, 为输入管的失调方差;

为输入管的失调方差; 为负载管的失调方差;AVTN,AVTP和AWLN,AWLP分别是与具体工艺相关的阈值电压失调因子和尺寸失调因子,在特定工艺下为常数,随着工艺制程的进步,其值随之减小。由式(6)可知,比较器的失调与晶体管的尺寸成反比,因此为了较小的失调,应适度地增加晶体管尺寸,但同时会导致寄生效益增加,故需折衷考虑。

为负载管的失调方差;AVTN,AVTP和AWLN,AWLP分别是与具体工艺相关的阈值电压失调因子和尺寸失调因子,在特定工艺下为常数,随着工艺制程的进步,其值随之减小。由式(6)可知,比较器的失调与晶体管的尺寸成反比,因此为了较小的失调,应适度地增加晶体管尺寸,但同时会导致寄生效益增加,故需折衷考虑。

2 应用Flip-around采样保持电路验证

电容翻转型(Flip-around)采样保持电路由于反馈系数β较大,等效到输出的噪声也相应减小,同时与传统的电荷传输型采样保持电路相比,其功耗更低。因此采用此结构对新型开关进行验证。

图5是采用电容翻转型采样保持电路的结构。为有效地抑制直流偏置和衬底噪声,同时减小偶次谐波失真,提高线性度,采用全差分输入输出结构;又由于CMOS开关固有的非理想效应,如沟道电荷注入以及栅极时钟馈通等,这会造成输入与输出之间的误差,需采用下级板采样技术克服。为与普通CMOS对管开关对比,进行2次FFT仿真,其中图5中的输入开关S0分别采用两种不同的采样开关,即普通的CMOS对管开关和本文设计的采样开关。两种情况下其他开关均使用普通单管开关。

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)