电源完整性设计1

时间:02-07

来源:互联网

点击:

电感上的电压。如果这一值接近2V,可能会被第二个非门判断为逻辑1,从而发生逻辑错误。

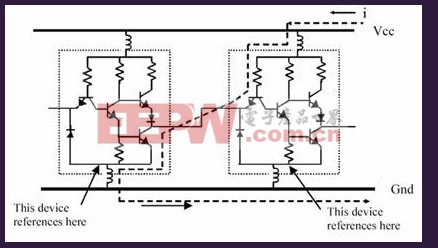

图8 级联的非门

寄生电感可能引起电路逻辑错误,那么如何解决这一问题?

图9展示了一种解决方法。把电容紧邻器件放置,跨接在电源引脚和地引脚之间。正常时,电容充电,存储一部分电荷。当非门发生翻转瞬间,电容放电,形成瞬间的浪涌电流,方向如图9中虚线所示。这样电路转换所需的瞬态电流不必再由VCC提供,电容相当于局部小电源。因此电源端和地端的寄生电感被旁路掉了,寄生电感在这一瞬间没有电流流过,因而也不存在感应电压,这就保证了第一个非门输出信号的逻辑电平值的正确性。

图9 局部去耦

所需电容可能不是一个,通常是两个或多个电容并联放置,减小电容本身的串联电感,进而减小电容充放电回路的阻抗。电容的摆放、安装距离、安装方法、电容选择等问题,本文后面会详细介绍。

很多芯片制造商在参考设计中给出的都是这种局部去耦方式,但并不是说这种方式就是最优的。芯片商关心的是如何提高他所提供的特定器件的性能,也就是说,着眼点在器件本身,并没有从整个电路系统的角度来处理电源去耦的问题。有时你会发现,对每一个的电源和地引脚都单独去耦是不现实的,可能是空间限制,放不下如此多的电容,也可能是成本限制。因此对于板级集成的工程师来说,除了要熟悉局部去耦的方法外,还要深入研究如何从整个电源分配系统的角度进行电源去耦设计。

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)