电源完整性设计1

装谐振频率,而不是自谐振频率,因为我们关注的是电容安装到电路板上之后的表现。

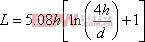

电容在电路板上的安装通常包括一小段从焊盘拉出的引出线,两个或更多的过孔。我们知道,不论引线还是过孔都存在寄生电感。寄生电感是我们主要关注的重要参数,因为它对电容的特性影响最大。电容安装后,可以对其周围一小片区域有效去耦,这涉及到去耦半径问题,本文后面还要详细讲述。现在我们考察这样一种情况,电容要对距离它2厘米处的一点去耦,这时寄生电感包括哪几部分。首先,电容自身存在寄生电感。从电容到达需要去耦区域的路径上包括焊盘、一小段引出线、过孔、2厘米长的电源及地平面,这几个部分都存在寄生电感。相比较而言,过孔的寄生电感较大。可以用公式近似计算一个过孔的寄生电感有多大。 公式为

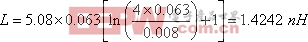

其中:L是过孔的寄生电感,单位是nH。h为过孔的长度,和板厚有关,单位是英寸。d为过孔的直径,单位是英寸。下面就计算一个常见的过孔的寄生电感,看看有多大,以便有一个感性认识。设过孔的长度为63mil(对应电路板的厚度1.6毫米,这一厚度的电路板很常见),过孔直径8mil,根据上面公式得:

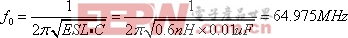

这一寄生电感比很多小封装电容自身的寄生电感要大,必须考虑它的影响。过孔的直径越大,寄生电感越小。过孔长度越长,电感越大。下面我们就以一个0805封装0.01uF电容为例,计算安装前后谐振频率的变化。参数如下:容值:C=0.01uF。电容自身等效串联电感:ESL=0.6 nH。安装后增加的寄生电感:Lmount=1.5nH。

电容的自谐振频率:

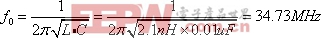

安装后的总寄生电感:0.6+1.5=2.1nH。注意,实际上安装一个电容至少要两个过孔,寄生电感是串联的,如果只用两个过孔,则过孔引入的寄生电感就有3nH。但是在电容的每一端都并联几个过孔,可以有效减小总的寄生电感量,这和安装方法有关。

安装后的谐振频率为:

可见,安装后电容的谐振频率发生了很大的偏移,使得小电容的高频去耦特性被消弱。在进行电路参数设计时,应以这个安装后的谐振频率计算,因为这才是电容在电路板上的实际表现。

安装电感对电容的去耦特性产生很大影响,应尽量减小。实际上,如何最大程度的减小安装后的寄生电感,是一个非常重要的问题,本文后面还要专门讨论。

电源完整性设计(7)局部去耦设计方法

局部去耦设计方法

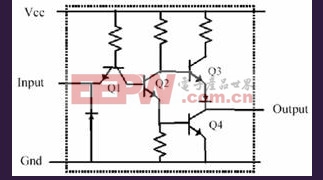

我们从一个典型逻辑电路入手,讨论局部退耦设计方法。图7是典型的非门(NOT GATE)电路。当输入(Input)低电平时,Q1打开,拉低Q2的基极,因此Q4的基极被拉低,Q3打开,输出(Output)高电平。

图7 非门内部逻辑

实际电路设计中,器件之间相互连接构成完整系统,因此器件之间必然存在相互影响。作为例子,我们级联两个非门,如图8所示,看看两个器件之间怎样相互影响。理想的情况应该是:第一个非门输入逻辑低电平(逻辑0),其输出为高电平,第二个非门输入为第一个的输出,也为高电平,因此第二个非门输出低电平。

为保证逻辑电路能正常工作,表征电路逻辑状态的电平值必须落在一定范围内。比如对于3.3V逻辑,高电平大于2V为逻辑1,低电平小于0.8V为逻辑0。当逻辑门电路的输入电平处于上述范围内时,电路能保证对输入逻辑状态的正确判断。当电平值处于0.8V到2V之间时,则不能保证对输入逻辑状态的正确判断,对于本例的非门来说,其输出可能是逻辑0,也可能是逻辑1,或者处于不定态。因此输入电平超出规定范围时,可能发生逻辑错误。

逻辑电路在设计时采用了很多技术来保证器件本身不会发生这样的错误。但是,当器件安装到电路板上,板级系统的其他因素仍可能导致类似错误的发生。图8中级联的两个非门共用电源端Vcc和接地端GND。Vcc到每个非门供电引脚间都会存在寄生电感,每个非门的地引脚到GND之间也同样存在寄生电感。在实际板级电路中设计中,寄生电感不可避免,电源平面、地平面、过孔、焊盘、连接焊盘的引出线都会引入额外的寄生电感。图8已经画出了电源端和地端的寄生电感。当第一个非门输入高电平,其输出低电平。此时将会形成图中虚线所示的电流通路,第一个非门接地处寄生电感上的电压为:V=L*di/dt。这里i为逻辑转换过程形成的瞬态电流。如果电路转换过程非常快(高速器件内部晶体管转换时间已经降到了皮秒级),di/dt将是个很大的值,即使很小的寄生电感L也会在电感两端感应出很大的电压V。对于一些大规模逻辑芯片,接地引脚是内部非常多的晶体管共用的,这些晶体管同时开关的话,将产生很大的瞬态电流,再加上极快的转换时间,寄生电感上的感应电压更大。此时第一个非门的输出信号电平为:非门本身低电平电压+寄生

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)