混合型多电平逆变器电路设计研究

时间:03-07

来源:互联网

点击:

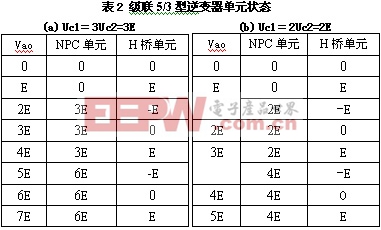

文献[11]提出了基于NPC三电平变换单元与H桥变换单元级联的不对称型逆变器(Asymmetric Inverter),单相拓扑结构如图2(b)所示。该电路高压NPC逆变单元采用的是 IGCT 器件,低压H桥单元器件采用的是IGBT 开关器件。其中高压3电平NPC逆变单元是主要逆变电路,Uc1为3E,这部分电路给输出提供了主要的电平电压和大部分输出功率,因此将NPC逆变单元称为主逆变单元;低压的 H 桥逆变电路单元则是辅助逆变电路,Uc2为E,这部分电路给输出提供了辅助改善波形的电平电压和小部分输出功率,因此将这部分逆变电路称为辅助逆变单元。在功率器件选用上,该电路采用了一种组合的方法,同时利用了两种不同开关器件的优点:IGCT的高阻断能力和IGBT的快速开关能力。但该电路在相电压输出为+2E或者-2E时,辅助逆变单元将输出对应的反相电压-1E或者+1E,在有功应用中,也会出现电流倒灌现象。如果Uc1为2E,Uc2为E,则可避免电流倒灌现象。

4、混合型逆变器拓扑结构设计方法要点

由前面分析可知,混合型逆变器存在高压单元电压应力过高、低压单元电流倒灌的问题。为了解决以上问题,在设计时可从以下两方面进行改进:

(1)克服高压单元功率器件电压应力过高问题

选择高阻断能力器件(如IGCT、GTO)或选择二极管箝位型逆变单元作为高压逆变单元(如二极管箝位型三电平或五电平结构)。这两种方法均可克服高压单元功率器件电压应力过高的问题,但由于高阻断能力的功率器件成本高、开关频率低,从而影响了系统的成本及输出波形的质量,而在逆变单元电压等级一定的情况下,NPC逆变臂功率器件的电压应力却是H桥单元的一半,可以显著降低功率器件的电压应力。因此,选择二极管箝位型逆变单元作为高压逆变单元是一种更加值得推荐的方法。

(2)消除低压单元电流倒灌问题

由于混合型逆变器在选取电压比较大时,会产生电流倒灌现象,因此在设计过程中,可选取适当的电压比以提供消除电流倒灌现象所需的冗余状态,并使得各电平台阶阶跃也限定在1E之内。以图2(b)电路为例,采用Matlab对该电路进行了仿真,仿真结果如图3,其中调制波频率为50Hz。根据公式(1)可知,两逆变单元电压关系可为Uc1=3Uc2 =3.3kV和Uc1=2Uc2 =3.0kV两种情况,相电压Vao输出分别为9电平和7电平(如图3(a)),两种情况单元1和单元2输出电压波形如图3(b)和图3(c)。从图3(c)可看出,当Uc1=3Uc2,单元1输出电压为正时,单元2输出电压为1.1kV、0kV、-1.1kV三种情况,在单元2输出-1.1kV时,则会与单元1输出3.3kV电压形成环流,出现电流倒灌现象,降低了逆变器输出功率,并导致单元2直流侧电位平衡,增加了输出相电压Vao的谐波含量(如图3(d)所示,THD为6.58%),降低了Vao的质量;而Uc1=2Uc2时,虽然Vao为7电平,但从图3(b) 与图3(c)看出,不会出现电流倒灌现象,Vao的THD降至3.51%。

以上分析及仿真结果表明:Uc1=2Uc与Uc1=3Uc2相比,在输出相电压Vao大致相同(分别为4.5kV和4.4 kV)的情况下,虽然Vao从9电平降为7电平,但低次谐波的幅值却显著降低,输出电压的质量得到了较大的提高(THD从6.58%降至3.51%),高压单元功率器件电压应力也有所下降(从1.65kV降至1.5kV)。

5、结论

本文针对混合电平式逆变器和混合单元式逆变器存在的高压单元功率器件电压应力过高、低压单元电流倒灌的问题,提出了高压单元采用二极管箝位型拓扑结构,选取各单元适当电压比的设计方法,经分析及仿真实验表明,该方法在克服电压应力过高、消除低压单元电流倒灌方面是有效的。

参考文献:

1.Rodriguez.J,Lai.J.S,Peng.F.Z. Multilevel Inverters:A Survey of Topologies, Control, and Applications[J]. IEEE Trans Indus Electron, 2002,49(4):724-737

2.Tolbert.L.M, Peng.F.Z,, Habetler.T.G. Multilevel converters for large electric drives[J]. IEEE Trans. Ind. Applicat. 1999,35(1):36-44

3.A. Nabae, I. Takahashi, and H. Akagi, A New Neutral-Point Clamped PWM Inverter[A], IEEE IAS. 1980:761-766.

4.T.A. Meynard, H. Forch. Multi-level conversion: high voltage choppers and voltage-source inverters[A]. IEEE PESC 1992:397-403

5.Madhav D. Manjrekar, Thomas A. Lipo. A hybrid multilevel inverter topology for drive applications[A]. IEEE APEC 1998:523-529.

6.T. A. Lipo and M. D. Manjrekar. Hybrid topology for multilevel power conversion [P]. U. S. Patent 6005788, 1999

7.Keith Corzine, Yakov Familiant. A New Cascaded Multilevel H-Bridge Drive[J], IEEE Trans. Power Electron, 2002,17(1):125-131

8.Cassiano Rech, Humberto Pinheiro, Hilton A. Gründling, etc. Analysis and comparison of hybrid multilevel voltage source inverters[A]. IEEE PESC 2002:491-496

9.M.R.Pavan Kumar, J.M.S.Kim, A hybrid multi-level switching converter for ring-magnet power supplies[J]. IEEE Trans. Nuclear Science, 1996, 43(3):1876-1883.

10.丁凯 邹云屏 王展 吴智超等,一种适用于高压大功率的新型混合二极管钳位级联多电平变换器[J].中国电机工程学报, 2004.24(9):62-67

11.Peter K. Steimer,Madhav D. Manjrekar. Practical medium voltage converter topologies for high power applications[A]. IEEE IAS 2001:1723-1730

- 帮你快速入门拓扑结构之正激(12-07)

- 两级拓扑结构的离网型光伏逆变器设计(06-28)

- 选取降压拓扑结构开关电源电感器的基本要点(01-17)

- 电源拓扑结构之LLC谐振及拓扑结构的影响(12-27)

- 技术知识学堂:电源的拓扑结构大揭秘之电源篇(12-27)

- 电源拓扑结构之入半桥结构及门级正激结构(12-27)