使电源系统各部分的阻抗与目标阻抗逼近。对于去耦电容,必须考虑电容的寄生参数,定量的计算出去耦电容的个数以及每个电容的容值和具体放置位置,尽量做到电容一个不多,一个不少。在Cadence仿真工具中,将接地反弹称为同步开关噪声(Simultaneous switch noise)。在仿真时将电源间的寄生电感、电容和电阻, 以及器件封装的寄生电感、电容和电阻都做考虑,结果比较符合实际情况。还可以根据系统使用的电路类型与工作频率,设置好期望的相关指标参数后,计算出合适的电容大小以及最佳的布放位置,设计具有低阻抗的接地回路来解决电源完整性问题。

3 高速PCB的设计方法

3.1 传统的设计方法

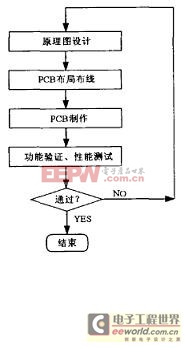

如图1是传统的设计方法,在最后测试之前,没有做任何的处理,基本都是依靠设计者的经验来完成的。在对样机测试检验时才可以查找到问题,确定问题原因。为了解决问题,很可能又要从头开始设计一遍。无论是从开发周期还是开发成本上看,这种主要依赖设计者经验的方法不能满足现代产品开发的要求,更不能适应现代高速电路高复杂性的设计。所以必须借助先进的设计工具来定性、定量的分析,控制设计流程。

图1 传统高速设计流程

3.2 Cadence设计方法

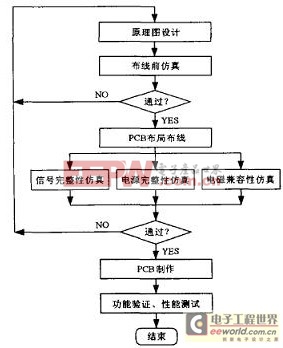

现在越来越多的高速设计是采用一种有利于加快开发周期的更有效的方法。先是建立一套满足设计性能指标的物理设计规则,通过这些规则来限制PCB布局布线。在器件安装之前,先进行仿真设计。在这种虚拟测试中,设计者可以对比设计指标来*估性能。而这些关键的前提因素是要建立一套针对性能指标的物理设计规则,而规则的基础又是建立在基于模型的仿真分析和准确预测电气特性之上的,所以不同阶段的仿真分析显得非常重要。Cadence软件针对高速PCB的设计开发了自己的设计流程,如图2它的主要思想是用好的仿真分析设计来预防问题的发生,尽量在PCB制作前解决一切可能发生的问题。与左边传统的设计流程相比,最主要的差别是在流程中增加了控制节点,可以有效地控制设计流程。它将原理图设计、PCB布局布线和高速仿真分析集成于一体,可以解决在设计中各个环节存在的与电气性能相关的问题。通过对时序、信噪、串扰、电源结构和电磁兼容等多方面的因素进行分析,可以在布局布线之前对系统的信号完整性、电源完整性、电磁干扰等问题作最优的设计。

图2 Cadence高速设计流程

4 结语

高速PCB设计是一个很复杂的系统工程,只有借助于那些不仅能计算设计中用到的每个元器件的物理特性和电气特性的影响及其相互作用,还必须能从设计的PCB中自动提取和建立模型,并且具有提供对实际设计操作产生动态特性描述的仿真器等强大功能的EDA软件工具,才能更全面地解决以上信号完整性、电磁干扰、电源完整性等问题。在具体设计过程中,在横向上要求各部分的设计人员通力合作,在纵向上要求设计的各个阶段综合考虑,把设计和仿真贯穿于整个设计过程,实现过程的可控性,具体指标的量化。只有这样才能做到高效的设计。

|