一种单级长延时电路的设计

时间:03-07

来源:互联网

点击:

入VIN低脉冲宽度为WIN,输出低脉冲宽度为WOUT,则有:

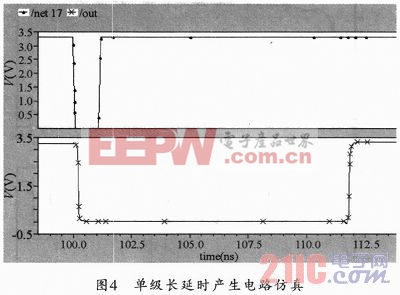

可以通过增大C1,减小IDC,TR增大,从而使WOUT增大,实现一级低脉冲展宽,且对输入脉宽的没有要求,很窄的输入脉冲也能直接被展到很宽。图4是该单级宽脉宽产生电路的仿真波形。

从仿真结果可知,输入一个1ns的低脉冲经过该电路直接展宽为11ns,而且展宽的宽度可以根据具体的要求,通过调整IDC、C1实现。且通过设计高精度IDC可以使延长做的很精准。

3 结束语

本文设计的单级长延时产生电路,在TSMC0.35微米工艺得到验证,用了极小的版图面积。此长延时产生电路,对输入的低脉宽宽度没有任何要求,而且一次展宽到位。同时可以通过设计精准的电流源和利用工艺偏差比较小的电容提高精度。此电路运用在异步时序控制信号产生电路里非常实用,随温度变化和工艺角变化相对较小。

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)