基于FPGA和DDS的数控信号源的设计与实现

ROM查找表结构如图4所示,其中头N个样值为正弦波数据,最后N个样值为三角波数据,中间是方波数据。若要输出正弦波,则从第1个存储单元开始查找;要输出方波,则从第N+1个单元开始查找,依次类推,图中N取32。

传统DDS技术中随着波形频率的增加,采样点数明显减少,使得波形质量也大大降低。采用这种方法,不管输出波形多大,采样点数都是固定的,从而避免以上问题。

2.3 地址信号发生器的设计

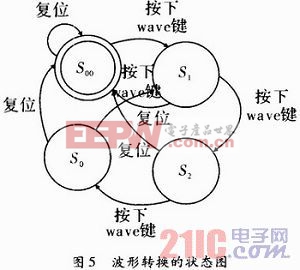

考虑到ROM的结构和每周期采样点数相同的需要,设计的地址信号发生器需要在提供ROM寻址的同时完成波形选择的功能。当波形选择键“wave”按下时,完成波形种类选择功能。波形种类转换采样状态机来完成,其状态图如图5所示。图中共有4种状态S00,S0,S1,S2。当复位信号有效时为S00状态,此时输出正弦波,否则每当按下“wave”键就从当前状态转换到下一状态。状态S0输出正弦波,状态S1输出方波,状态S2输出三角波。当“wave”键没有按下,且相位累加器溢出时,地址信号发生器就是一个N进制的计数器,使ROM表顺序地读出当前波形数据。

2.4 外围电路的实现

外围电路包括幅度控制、显示以及输入模块等部分。

幅度控制通过调节比例放大电路来实现。显示模块由LED数码管和指示灯组成,其中8位数码显示频率,指示灯显示波形种类。用动态扫描方式依次点亮8位数码管。

输入模块用于输出波形选择和波形频率设置,均由4×4键盘完成。波形选择只用一个按键完成,按下后循环选择“正弦波→方波→三角波→正弦波”,同时输出相应波形种类指示灯信号。

根据系统中DDS结构,输出波形的频率为

式(1)中,fclk为系统时钟频率;Fword为频率控制字;Mode为相位累计器的模,N为每种波形数据的字长。由于fclk,Mode,N均为定值,所以输出频率与相位控制是比例关系,可用一个乘法器来实现。文中取fclk=50 MHz,Mode=5×107,N=32,则f0=Fword/32,输出波形频率精度为0.03 Hz。根据采样定理,输出频率f0最高为fclk的1/2,但是实际上f0低于fclk的40%时,输出波形的稳定性才比较好。

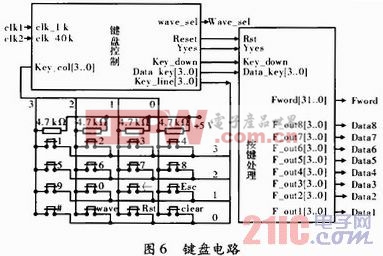

键盘电路如图6所示,由键盘、键盘控制和按键处理3部分组成。键盘控制完成键扫、按键去抖和按键标志产生功能。按键处理部分对数字键和功能键的处理。频率设置时,输入的数字作为波形的输出频率,并转换成对应的频率控制字送入DDS模块。设置频率的同时,输入的设置值送入显示模块显示。

按键说明:“←”键表示删除最后一位输入的数字,“esc”键表示放弃当前输入的数字,“#”键表示确定输入,“wave”键表示波形种类选择,“reset”键为复位键,“clear”键为清零键。输出频率设置操作为从键盘输入需要输出的频率值,最后按下确认键“#”即可。

3 系统仿真与验证

在QuartusIl开发平台中,将在FPGA中实现的各个模块连接起来得到系统顶层模块,其仿真结果如图7所示。仿真时系统时钟频率设置为与硬件系统时钟一样fclk=50 MHz,则时钟周期为20 ns。图7是在Mode=5×107,N=32,Fword=(E883CO)H时的仿真结果,其中图7(a),图7(b)和图7(c)分别是正弦波、方波和三角波的仿真波形,从仿真图中观察它们的波形周期均为2.1μs,即换算成频率是476.190 kHz。从图7(b)和图7(c)看出,波形转换快速,只需6个时钟周期即约为12.3μs。

系统FPGA芯片采用EP2C8Q208,系统时钟50 MHz。D/A转换采用8位无符号DAC0832集成电路,低通滤波器采用LM324集成电路和RC网络组成的有源低通滤波器。

系统仿真正确后,将设计代码下载到FPGA芯片中,然后用示波器测试输出波形结果如图8所示。其中图8(a)是在频率控制字与仿真图一致时,示波器的测量结果。从图8中看出,系统能够正确输出正弦波、方波和三角波,而且输出频率为7 MHz时波形质量依然良好。

4 结束语

介绍了一种基于FPGA和DDS技术的数控信号源的设计和实现方法,并给出系统仿真和硬件测试结果。设计方案主要在FPGA芯片内实现,外围电路简单。设计的系统能够输出正弦波、方波和三角波,输出波形在整个频率范围内波形质量均好,精度达0.03Hz。

设计 实现 信号源 数控 FPGA DDS 基于 相关文章:

- 3D IC设计打了死结?电源完整性分析僵局怎么破(09-21)

- 快速调试嵌入式MCU设计仿真的三大因素浅析(12-12)

- 访问电源参考设计库的众多理由(12-09)

- 开关电源设计中如何选用三极管和MOS管(12-09)

- 一款常见的车载逆变器设计电路图(12-09)

- 电子工程师必备:电源设计及电源测评指南(12-09)