高压元器件整合简化PoE用电装置设计[

要求,这些重要元器件的整合须使用一种能够提供高操作电压和在PSE设备与PD装置接口之间提供电气隔离的工艺技术。当然,它们相对于分立设计的成本也必须列入考虑。

开关稳压器的功率MOSFET

许多开关式稳压控制器都没有整合功率MOSFET,这虽能提供弹性的输入电压范围和输出功率范围,却必须以开关效率、电路板面积和成本最佳化为代价。由于PoE用电装置的输入电压范围(36~57V)和输出功率(12.95W最大值)都不算宽广,设计人员确实可将适当的开关功率FET整合到应用。

Rsp是一种优值(figure of merit),用来描述工艺技术的导通阻抗能力。RSP是MOSFET导通阻抗(RDS(ON))与总布局面积(不仅是门极)的乘积,其单位是Ωmm2。MOSFET的RSP越低,达到目标RDS(ON)所需的元器件就越小。外接式高压MOSFET经常采用RSP值相对较高的成熟工艺技术,这表示元器件必须很大才能提供很低的导通阻抗;除此之外,这类元器件多半需要较高的门极电压才能让信道完全反转(以及最低导通阻抗)。

使用外接式功率MOSFET时,高RSP和高门极电压是造成开关效率下降的两大因素。外接FET不仅会引入电路板寄生参数,庞大的元器件面积还会造成很大的门极电容,控制器在让FET导通或截止时都必须对这些电容进行充电与放电。由于开关功耗CgateVgate2成正比,面积过大的外接MOSFET可能增加PoE应用的耗电。

设计人员若能事先知道电压规格与输出功率范围,即可采用适当的工艺技术和面积最佳化的功率MOSFET以大幅减轻这些问题。设计人员可通过FET导通阻抗和门极面积的取舍发展出最佳元器件架构,再配合更低的门极电压以省下可观电力。只要把FET和控制电路整合到很小的封装,设计人员就能提供体积比分立解决方案还小的PD装置解决方案。

高压整合的工艺需求

bulk CMOS和BiCMOS等主流技术无法将最好的高电压、功率和效率组合提供给PD应用。另一方面,Silicon-on-Insulator(SOI)技术却能制造二极管和BJT等高效能接面元器件,同时提供功率MOSFET的面积与效率;除此之外,SOI还具备强大的高功率瞬时耐受性以及优异的内部噪声隔离能力,使得高质量功率元器件以及精准数字与模拟控制的整合更简单。深沟隔离和氧化埋层还能避免其他技术常见的寄生参数以及庞大的接面隔离阻障层。

理想PoE解决方案需要高压整合

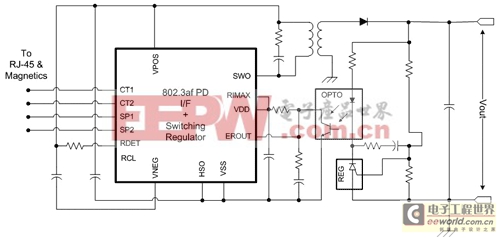

高压整合必须提供实际利益,这样对PoE用电装置设计人员才有价值。元器件用料的减少是很好的成本与电源转换效率指标,这两者都是设计人员能够实际感受到的好处。本文包含两款PoE PD电源管理元器件,一款是不包含高压元器件的传统解决方案(图1),另一款则采用前述SOI工艺(图2)。

图2 PoE PD接口和开关整流器

整合式浪涌抑制器还能使用较低的箝位电压,因此元器件不需采用崩溃电压较高的工艺。举例来说,标准SMAJ58A在Ipp=5A时的箝位电压约为94V,因此 PD接口元器件须使用能够承受100V的工艺技术。整合式瞬时抑制解决方案可以存取任何电路节点,进而让所有较大的瞬时电流都通过瞬时抑制二极管。举例来说,内部瞬时抑制器被触发后就会主动关闭热抽换接口和交换稳压器,防止具有破坏性的高能量瞬时电压进入下游电路。

通过别出心裁的高压电路设计和SOI工艺技术,厂商不仅能发展整合度更高的PD电源供应解决方案和省下超过18颗的外部元器件,还能提供媲美于分立解决方案的电源效率。

- TI基于UCD3138的高整合度新一代数字电源方案(12-07)

- 电源设计:整合电源管理与转换 简化电源系统设计(12-29)

- 反激式控制器将有源 PFC 功能电路整合在单级转换器(07-03)

- 电源设计小贴士 1:为您的电源选择正确的工作频率(12-25)

- 用于电压或电流调节的新调节器架构(07-19)

- 超低静态电流电源管理IC延长便携应用工作时间(04-14)